Hi,

we are developing a portable device to acquire 8 ECG channels at 500Hz. The system is based on the ADS1298 chip and a Cypress microcontroller. The whole system is powered by a LiPo battery. Here is what we are doing:

1. The ADS1298 is set into high-resolution mode and the output data rate is set to 500sps.

2. The gain of the PGA is set to 6

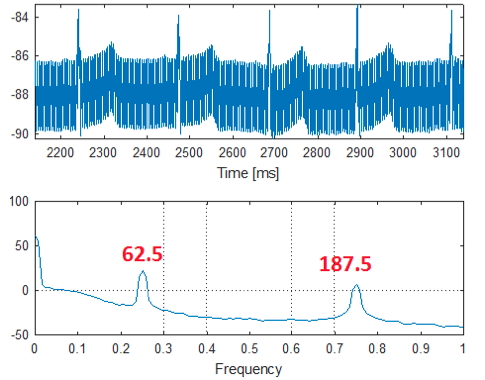

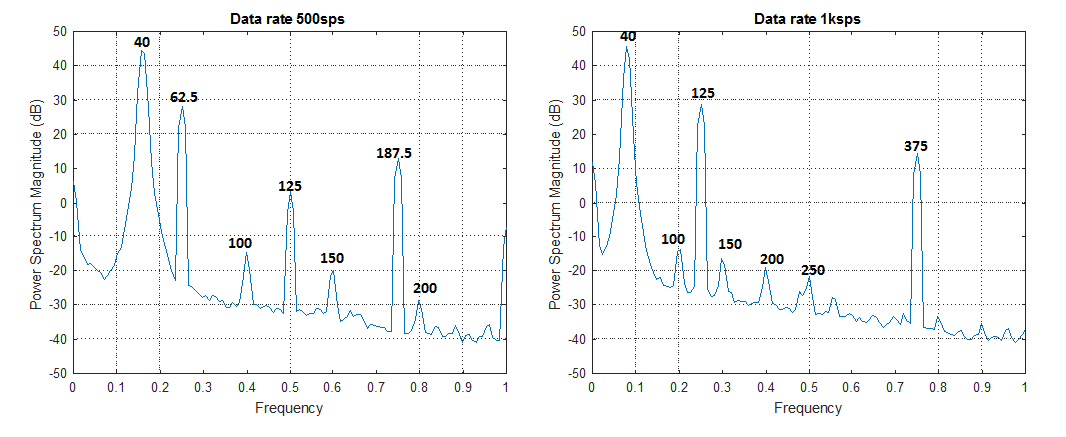

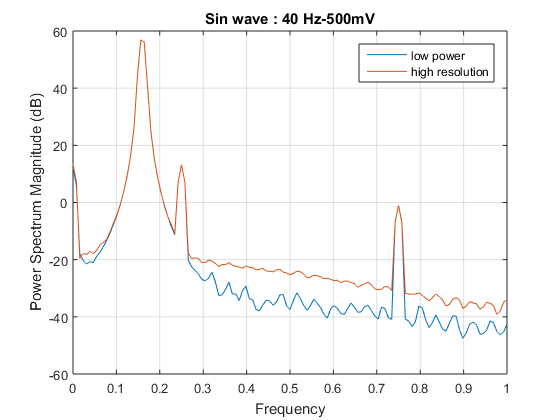

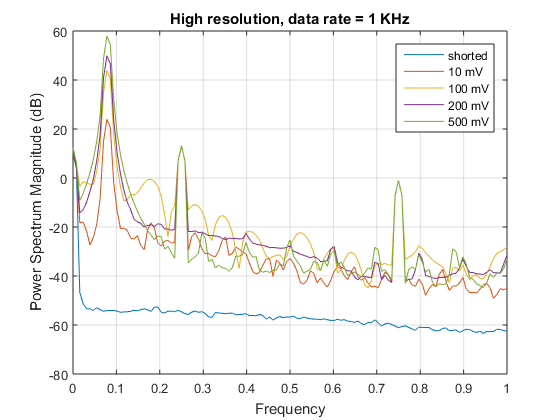

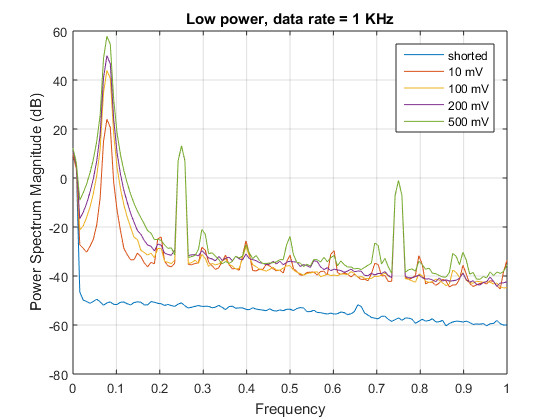

Whenever we try to acquire the ECG channels in this configuration, the signals appears very noisy. The analysis of the signals power spectrum shows different peaks at specific frequencies as shown by the following figure:

These peaks are always present regardless the environment noise or the channel analysed.

Is this caused by the ADS or we doing something wrong? Anyone else noticed this behaviour?

Thanks.