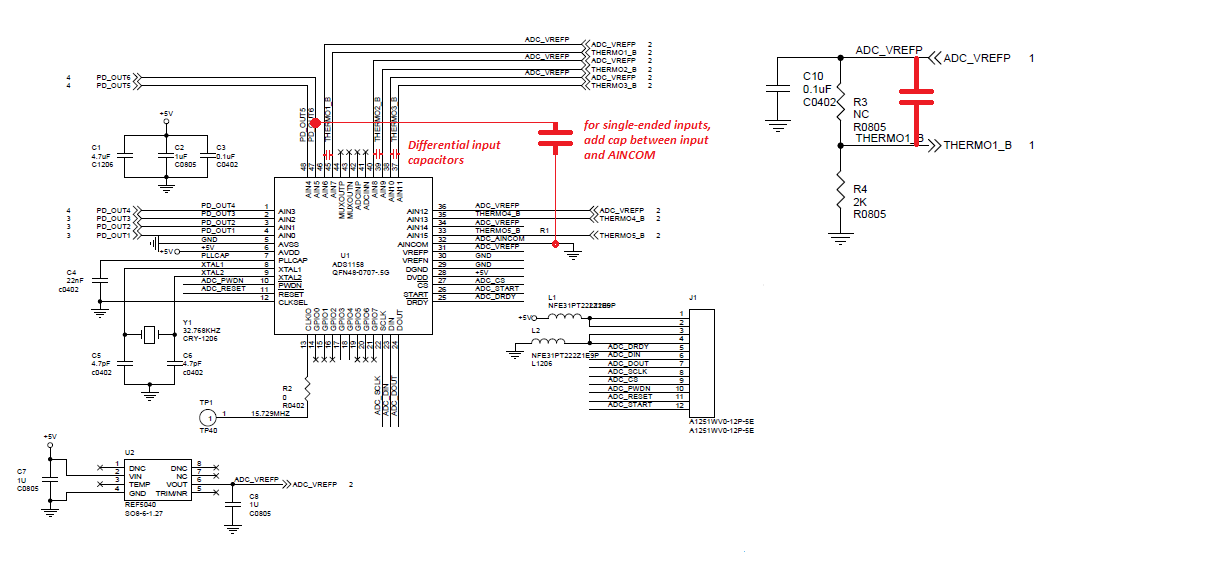

Other Parts Discussed in Thread: REF5025, REF5040, ADS1258, ADS1262

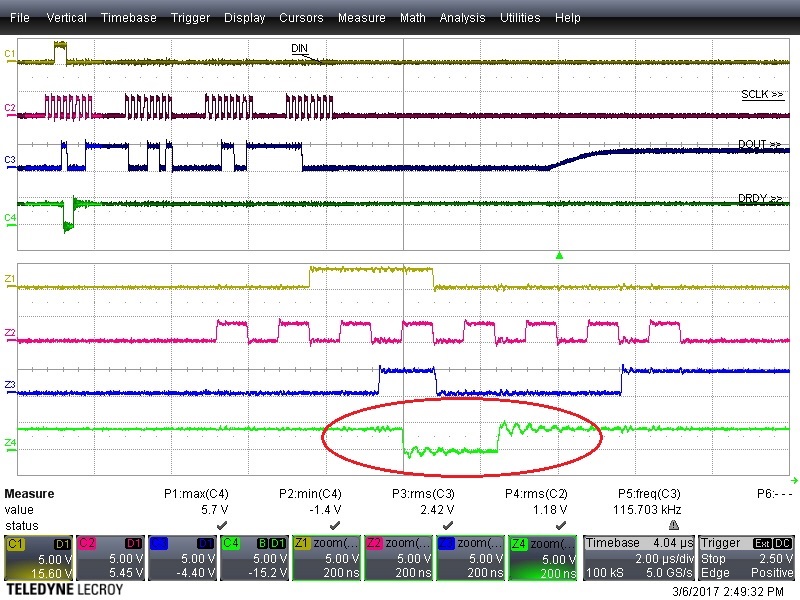

in our analog circuit, I found there was some cases that incorrect data were derived from ADS1158.

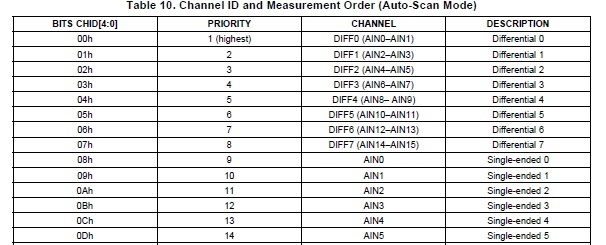

Thus, I use Tektronix function generator to generate a 300 mv signal. And I use channel AIN5 (0xD) of ADS1158 to measure it.

VREF: 4.96V

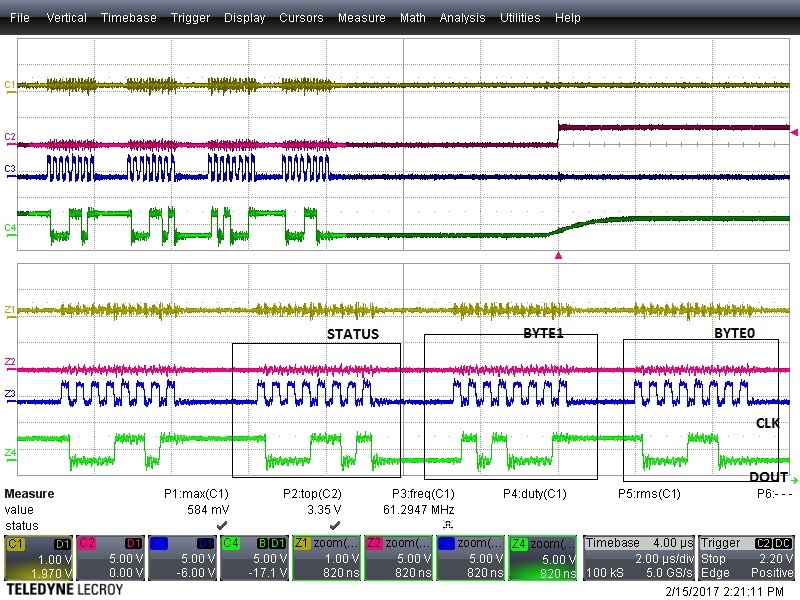

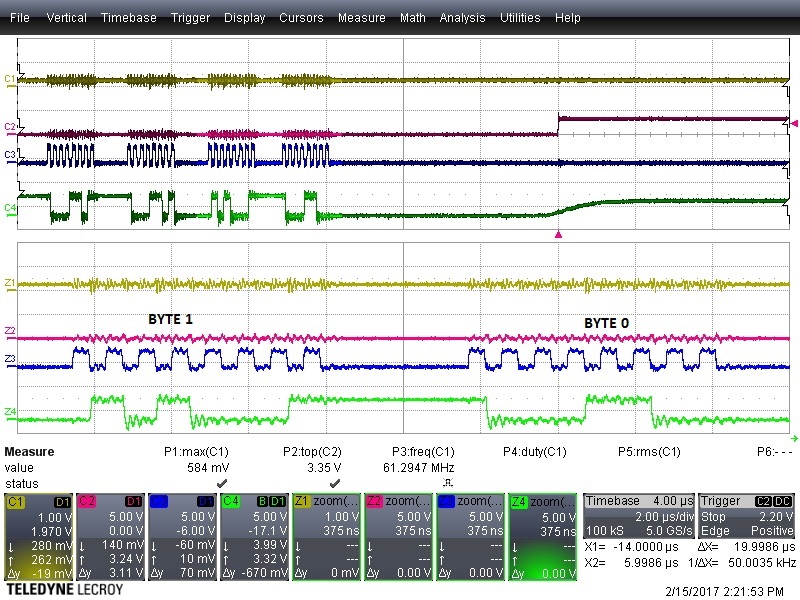

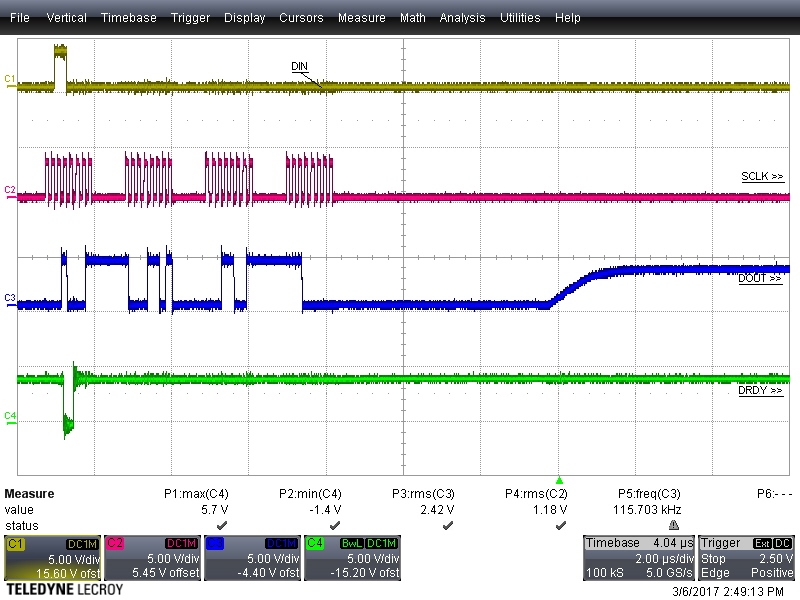

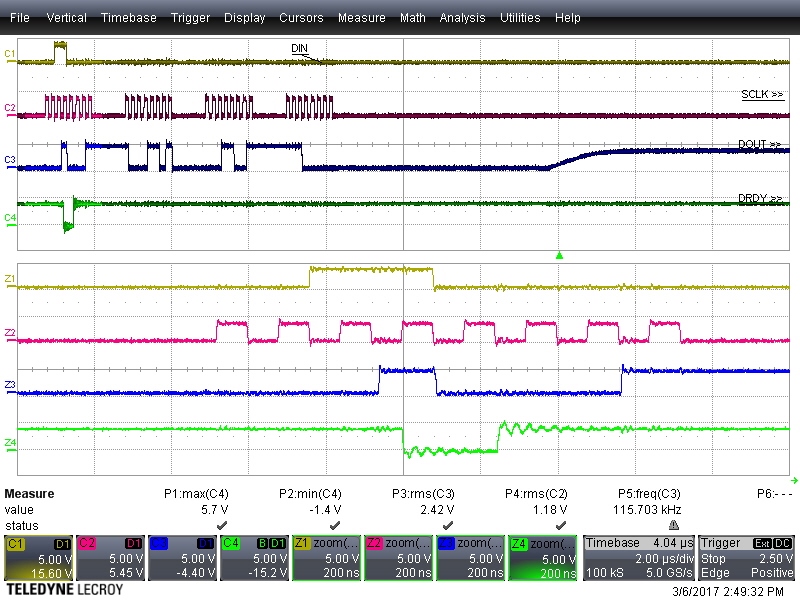

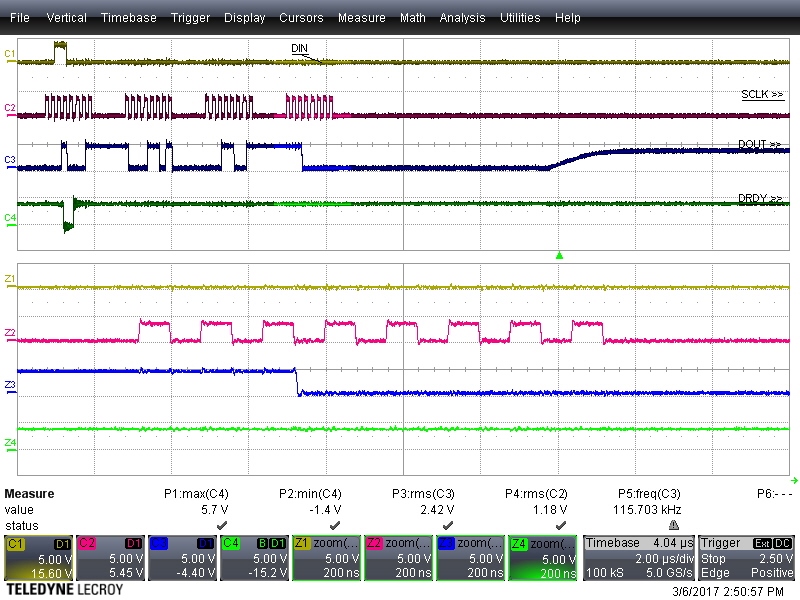

I useed a gpio pin to trigger the scope while the abnormal case happened.

in normal case, adc count are 2238~2278. (298.4mv ~ 303.73mv)

but in abnormal case, i got the big count, and it was not spi interface problem or calculation problem.

Because in scope, the signal output from ADS1158 actually sent that big value on DOUT pin

please check

STATUS BYTE: 0x8D (NEW & CHID = AIN5)

DATA BYTE1: 0x51

DATA BYTE0: 0x8C

data = 0x518C = 20876 --> 2783mv !!

and C1 is measured signal, from scope, its max is P1: max(C1) = 584mv

Please give some clues about this scenario. thanks

regards,

Ivan