Hello all,

I am trying to read data from ads8363 converter. I am able to write/read configuration register, but when it comes to reading adc readings I am getting all kinds of seemingly of random values, sometime correct values, sometimes some random data.

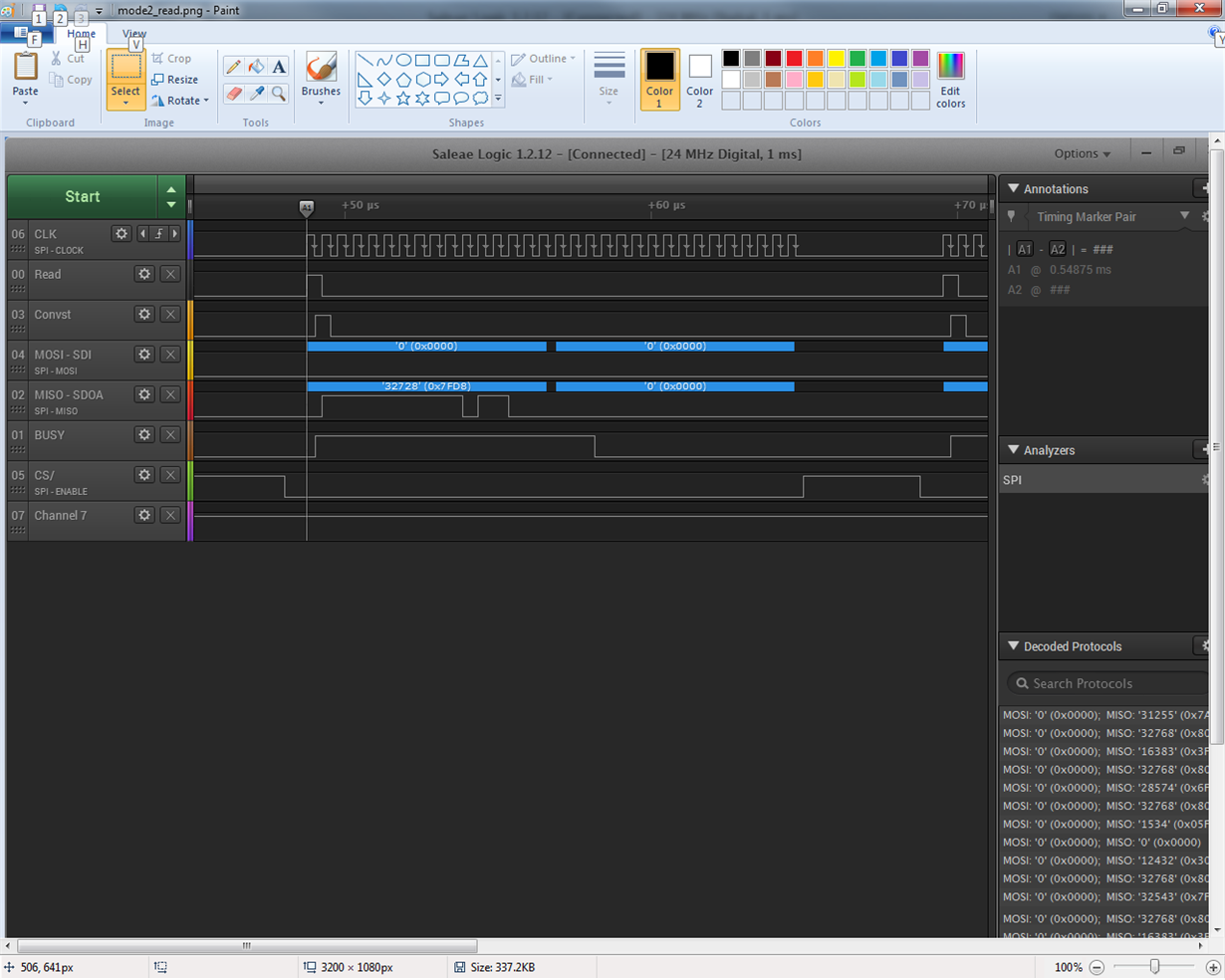

I am attaching here the file from the logic analyzer, I have doubts about my CONVST and RD signals. I set them up such that RD always come half-clock earlier than CONVST.

In my setup the RD signal is triggered by the raising edge of the first clock-pulse, and the RD lasts for one clock cycle. The CONVST starts on the falling edge of the first clock, half clock cycle later, and also lasts for one clock-cycle.

Is this OK ?

( I work in MODE II - M0=0, M1=1, with only SDOA active).