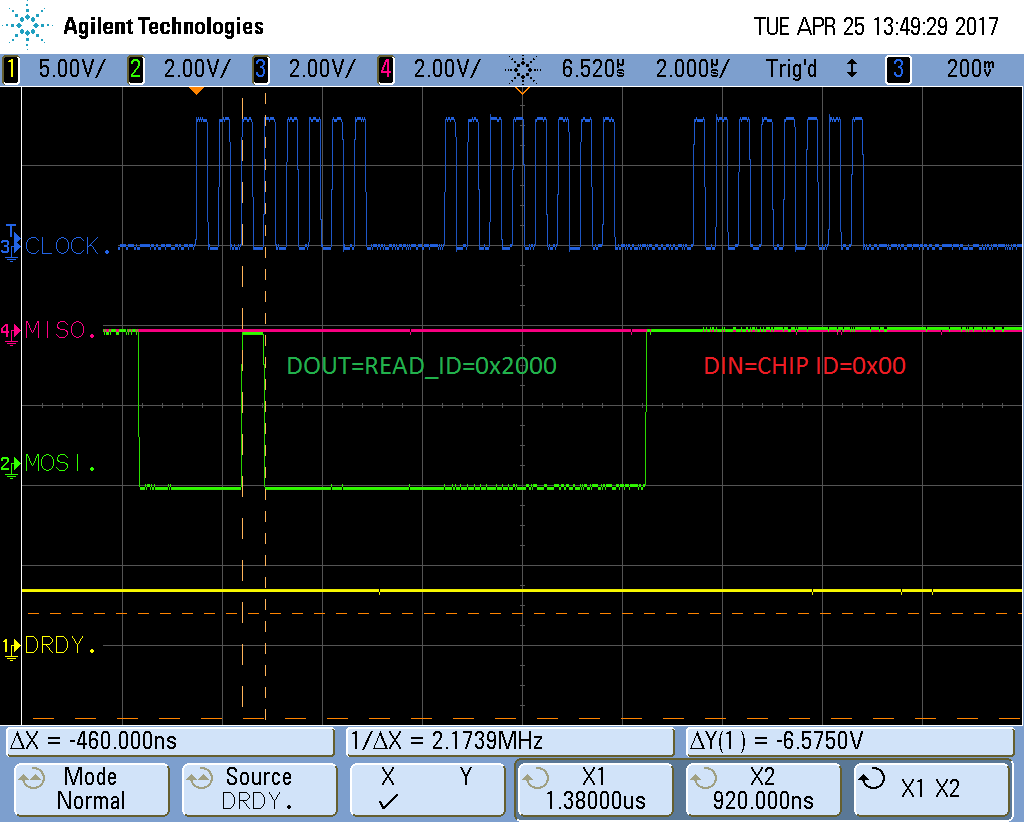

I have resetted my ADS1194 and sent a SDATAC command, after that I send a RREG(ID) command, but I don't get any response from ADS1194 which should be 0xB4. Attached is the oscop shot. Can you please help me debug this?( MOSI is DIN, MISO is DOUT)

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.