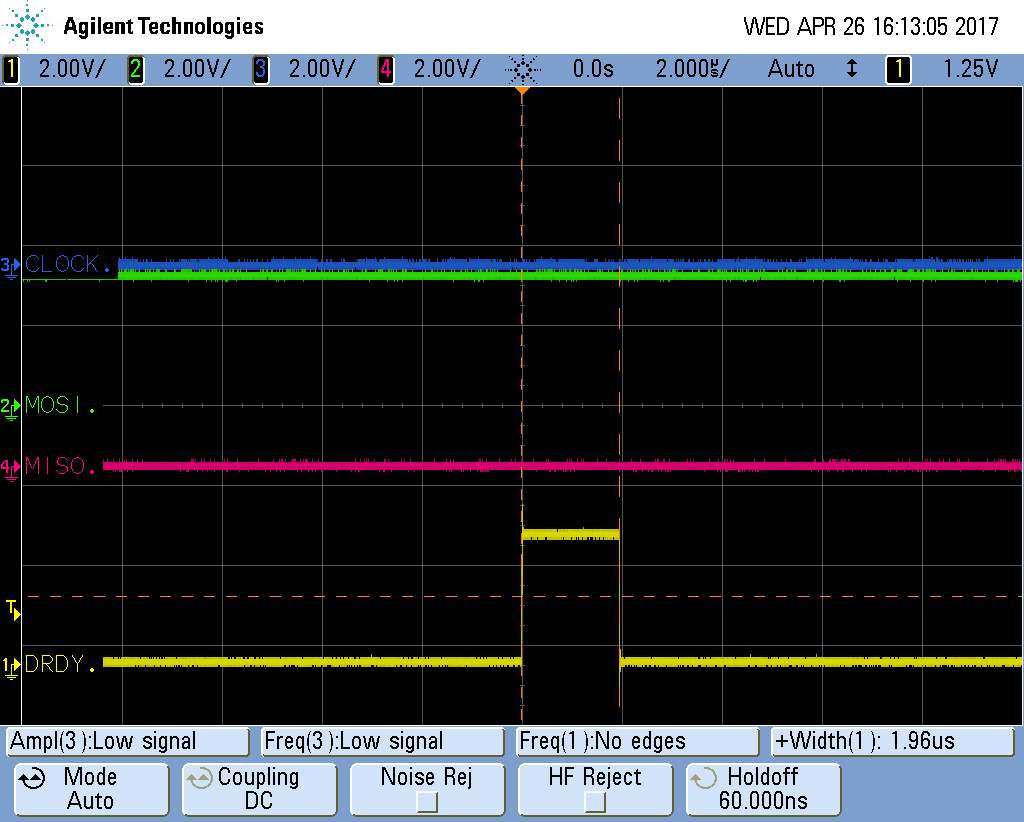

I have programmed the chip to RDATAC mode, but DRDY signal is not as datasheet which is normaly high and goes low for 1.96us when it has data ready. My DRDY is normaly low and goes high for 1.96us at the sampling rate frequency. Is this a problem of datasheet or my setup is not working correctly?

I also found some mistakes in Figure 58. First WREG CONFIG3 should be 0xC0 not 0x80. Second that WREG CONFIG2 shuld be 0x30 not 0x10.