Hello.

The datasheet says:

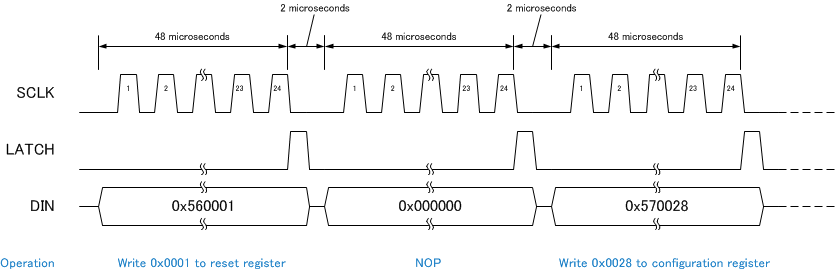

8.6.1.4 Reset Register

The DACx750 reset register is written to at address 0x56. Table 17 provides the description.

Table 17. Reset Register

DATA BIT(S): DB0

NAME: RESET

DEFAULT: 0

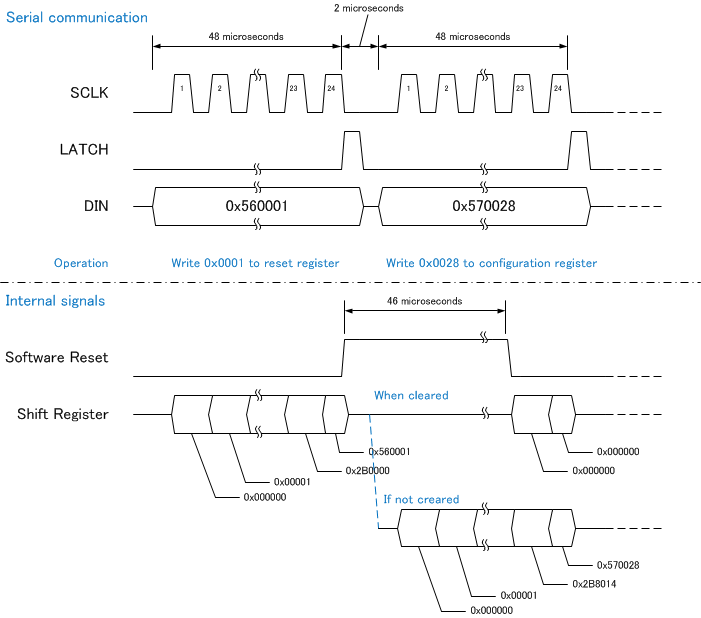

DESCRIPTION: Software reset bit. Writing 1 to the bit performs a software reset that resets all registers and the ALARM status to the respective power-on reset default value. After reset completes, the RESET bit clears itself.

Question:

How long does it take to complete the reset after writing 0x01 to the reset register?

Best Regards.