Hi, my name is Juan from Argentina.

I would like to use ADS1294 to make a project which constist on sensing eye blinking but I have some questions:

1) As regard to connection, I have two options:

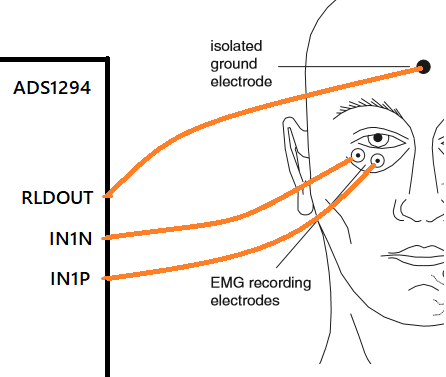

a-

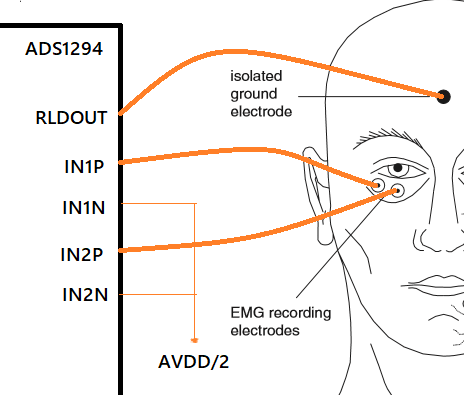

b-

I am considering to use an unipolar supply (0V - 5V), so I dont know if the two options are correct and which one is the best with this supply method. Could you help me?

2) In two pictures, I connect RLD electrode to RLDOUT but I read that it can connect to RLDIN and then this signal can be rerouting to any of channel input. What are the differences? Any advantage?

3) As regard to isolate the device from the human body, an optoisolator is recommend. Are they necessary in all inputs or only at RLDOUT? Do you have any CI to recommend in TI?

4) Before channel input, I am thinking to use a band pass filter (Low pass filter: 500Hz and High pass filter:28Hz). Is first order filter enough?

Thank you.