Other Parts Discussed in Thread: TLC5510A, ADS7884

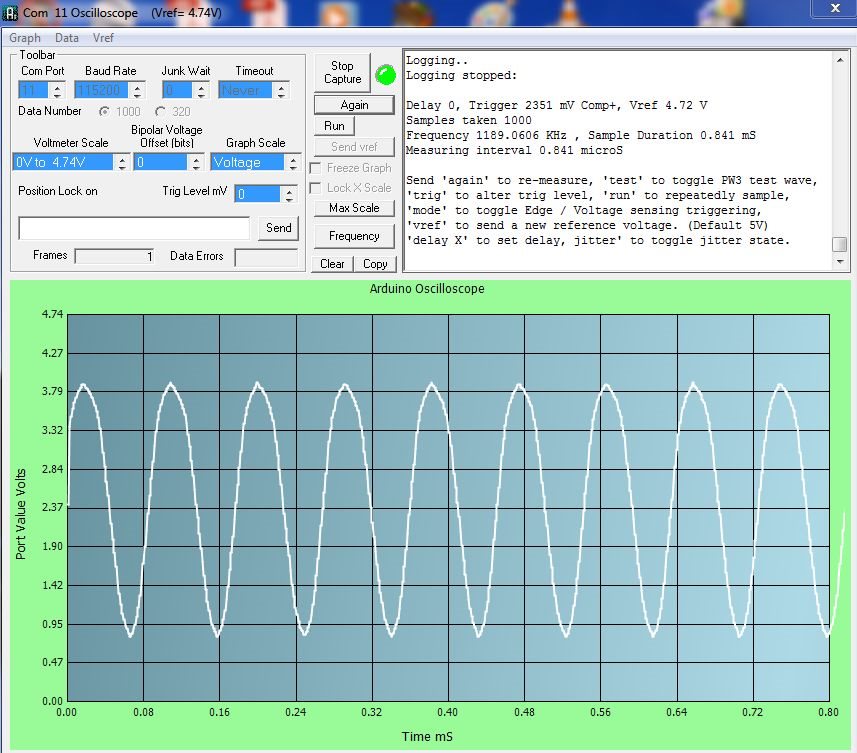

I have built an oscilloscope using the excellent TLV571 chip.

The results are good using Normal shutdown, however I cannot get Software shutdown to work.

Normal shutdown register settings:

INT OSC FAST, BINARY

CR1: B01010000

SOFTWARE START (D5), EOC (D4), INTERNAL CLOCK (D3), NORMAL (D2)

CRO: B00110000

I write CR1 before CRO, using the 1st 3 bits of a bi-directional port (C) to control the read (bit 2), write (bit1) and cs (0) lines:

I wait for the end of conversion line to go high on completion

cli();

PORTC = B00000110; // read high, WR high, CS low

__asm__("nop\n\t"); // wait one machine cycle (at 16 MHz)

// yielding a 62.5 ns (nanosecond) delay

PORTC = B00000100; // read high, WR low, CS low

__asm__("nop\n\t");

PORTC = B00000110; // read high, WR high, CS low - transfer data

__asm__("nop\n\t");

while ((PINC & econ) == 0 ); // wait for econ to go high

sei();

This all works and data can be read using the control port (C) to read data from port (PINA):

PORTC = B00000010; // RD low, WR high, CS low

PORTC = B00000110; // RD high, WR high, CS low

// wait for econ to go high

while ((PINC & econ) == 0 );

test = PINA;

This works. (Achieving a data rate of 1189.1 KHz)

However auto reset has a habit of kicking in whilst waiting for the input to trigger, rendering the first 2 data bytes from the TLV571 un-useable.

(The two reading issue is mentioned in the data sheet)

I can partially get round this by continually polling the adc. However this is not ideal.

I have tried changing cr0 to disable auto-shutdown.

B00110100 // cr0 SOFTWARE START (D5), EOC (D4), INTERNAL CLOCK (D3), software powerdown (D2)

The adc then returns a constant value.

I have no idea why.

Any ideas?

David