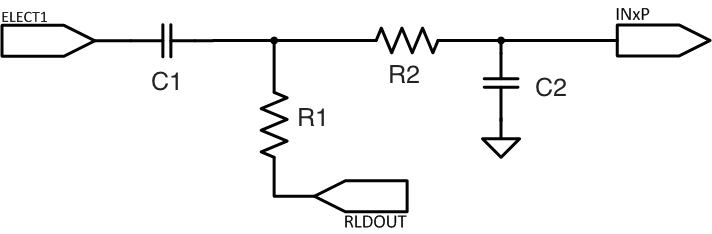

I've read on the forum about using RLDOUT/RLDINV for input bias and Ryan Andrews suggested the following:

If we label the capacitor and resisters from left to right as C1, R1, R2, C2. They are C1=0.1uf, R1=5Mohm, R2=51K and C2=47pf. So the first C1R1 high pass filter cutoff frequency is about 0.3Hz.

Same circuit for the INxN input as well.

What is the correct register settings for this RLD bias circuit to work properly?

Currently I have MISC2 register, RLDREF=1 so the input voltage would be biased to the middle (AVDD+AVSS)/2. Other settings related to RLD stayed at defaults.

The issue I'm facing now is that it will either get a few seconds of ECG signal about 2mv which is expected then just fall to 0mV flat, or simple stay at 0mv flat.

But if I remove R1, then ECG signal about 2mv would be captured continuously, of course it would DC drift without the bias pull up.

What could be the problem in the circuit or register programming?