Other Parts Discussed in Thread: ADS1246

Hi

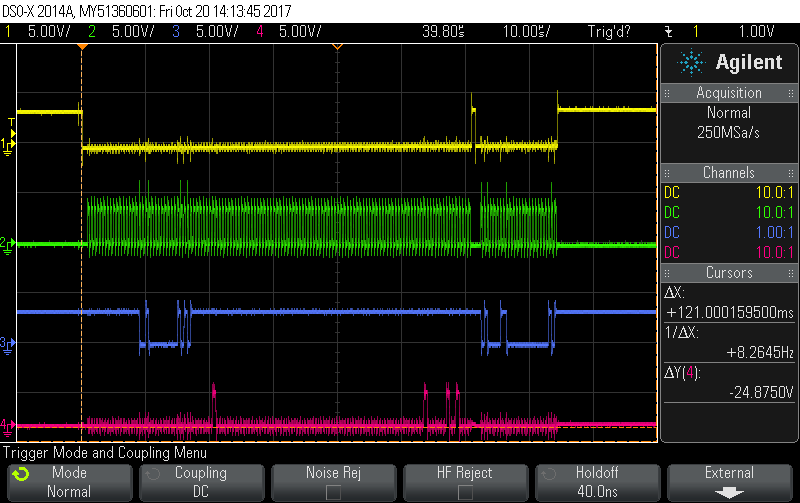

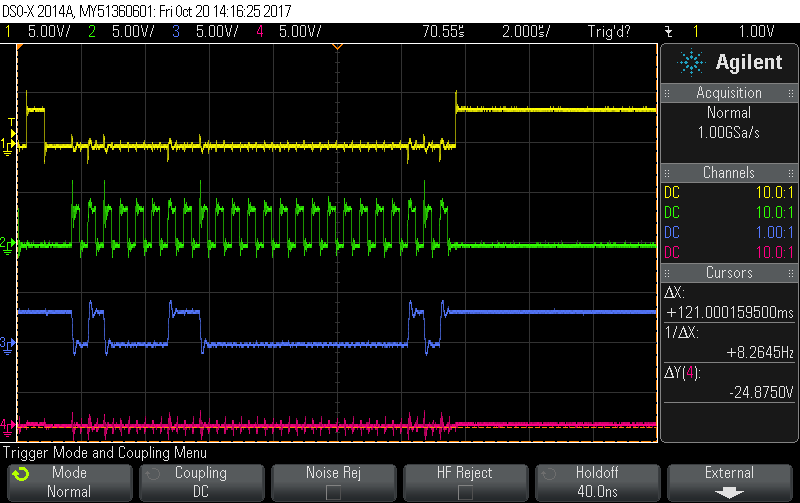

A write to the system control register (or any other register in the device) fails to update. I can however read the initialized values as per datasheet and they match! What setting can block a write to the configuration registers?

Perhaps my initialization sequence is wrong?

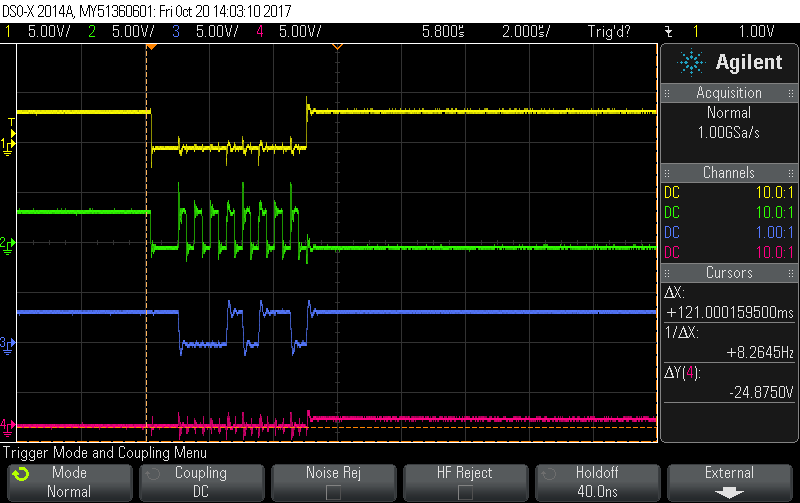

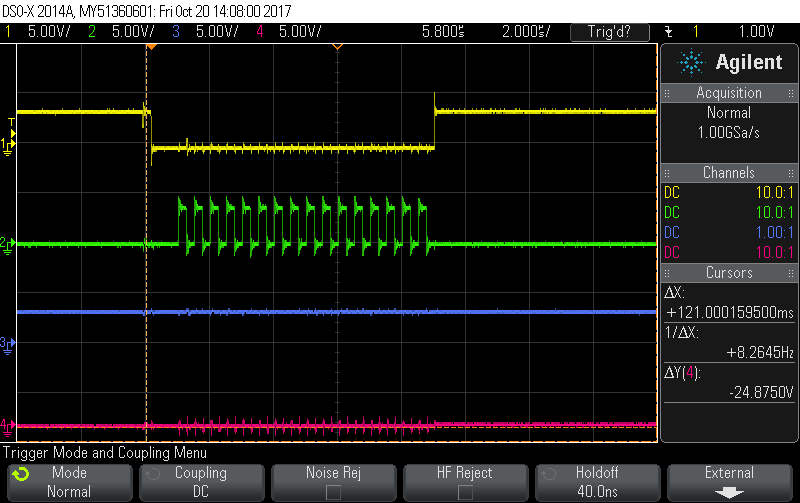

1 - Set START = 1, set RESET = 0;

2 - wait 20ms

3 - Set START = 1, set RESET = 1;

4 - wait 20ms //omitted this delay makes no difference

5 - send the command SDATAC //this will only take effect after the next READY signal

6 - wait for the READY signal

7 - Read the 16 bit answer to clear DOUT

8 - Read all the registers in one sweep (11) //this is just to see how they compare to the datasheet.

BCS = 0x01

VBIAS = 0x00

MUX1 = 0x00

SYS0 = 0x00

OFC0 = 0x00

OFC1 = 0x00

OFC2 = 0x00

FSC0 = 0x00

FSC1 = 0x00

FSC2 = 0x40

ID = 0x72

9 - write Control system register = 0x05 //set speed at 160SPS

10 - wait 40 microseconds

11 - read all 11 registers in one sweep to compare -> All the registers stay the same, the control register does not update!

Please advice.

Phlip