Hello all,

I am trying to interface ADS1292R with STM32F429 ARM processor via SPI. Circuit for ADS1292R is the same as ADS1292RECG-FE.

I am trying to read just ID register, so I am sending first opcode byte 20h and second opode byte 00h. Response is 73h ( which is correct ) but also 02h ( which is not correct ). I connected logic analyzer and I am seeing the same thing. Where is that 02h coming from?

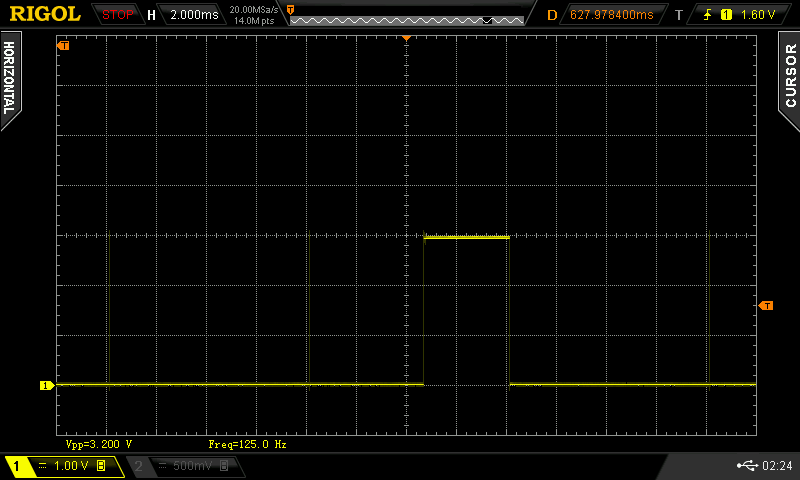

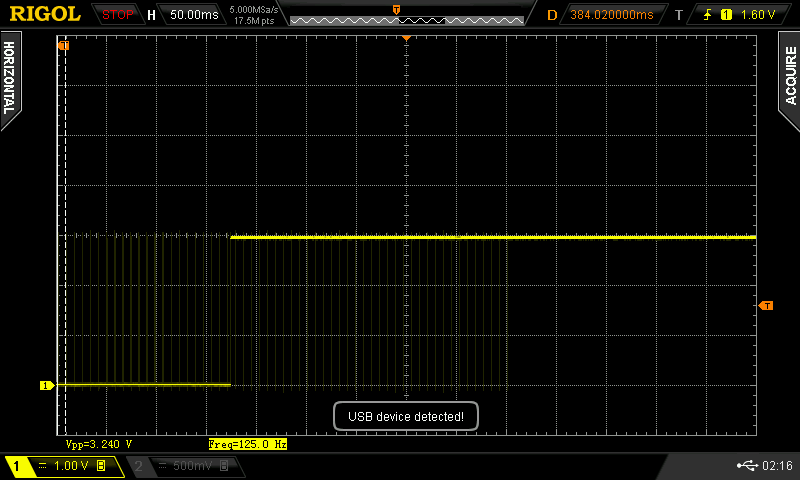

EDIT: I found out that 02h is data from CONFIG1 register. However I am still not sure why is ADS1292R sending data from two registers when I am using command to read just one register. Also if I send command to read two registers ( example from datasheet ), ADS1292R sends data from three registers. Is that a bug or am I doing something wrong? Also here is example of writing to register CONFIG1 and then requesting data from two registers, starting from register CONFIG1. It can be seen that ADS1292R sends data from three registers CONFIG1, CONFIG2 and LOFF.

Thanks in advance for any help,

Josip