Hello TI community,

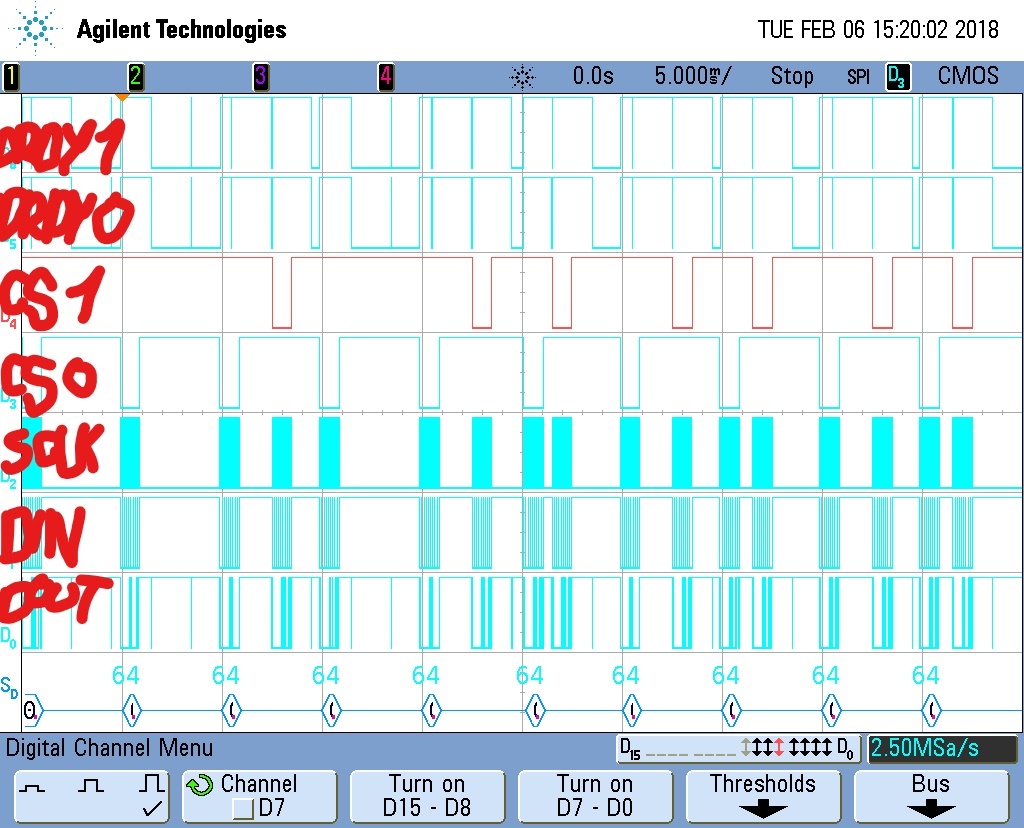

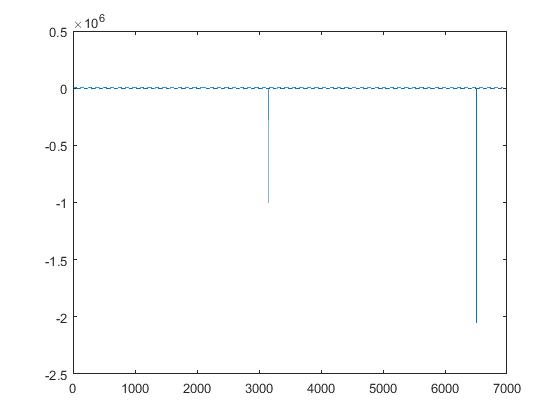

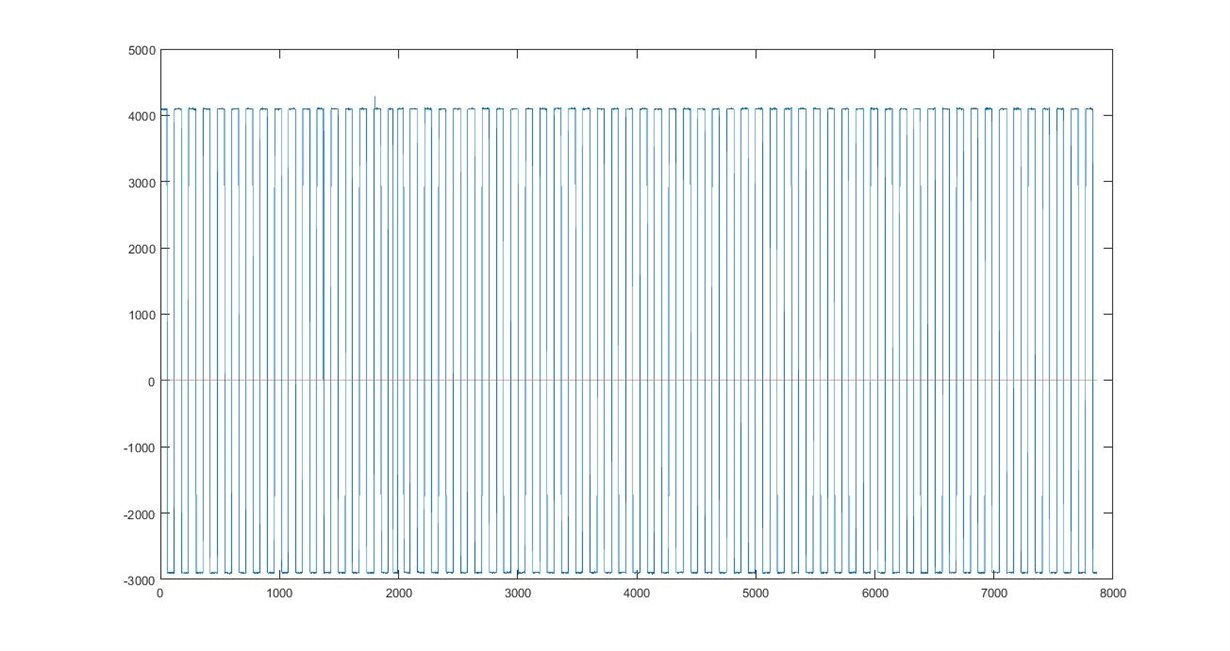

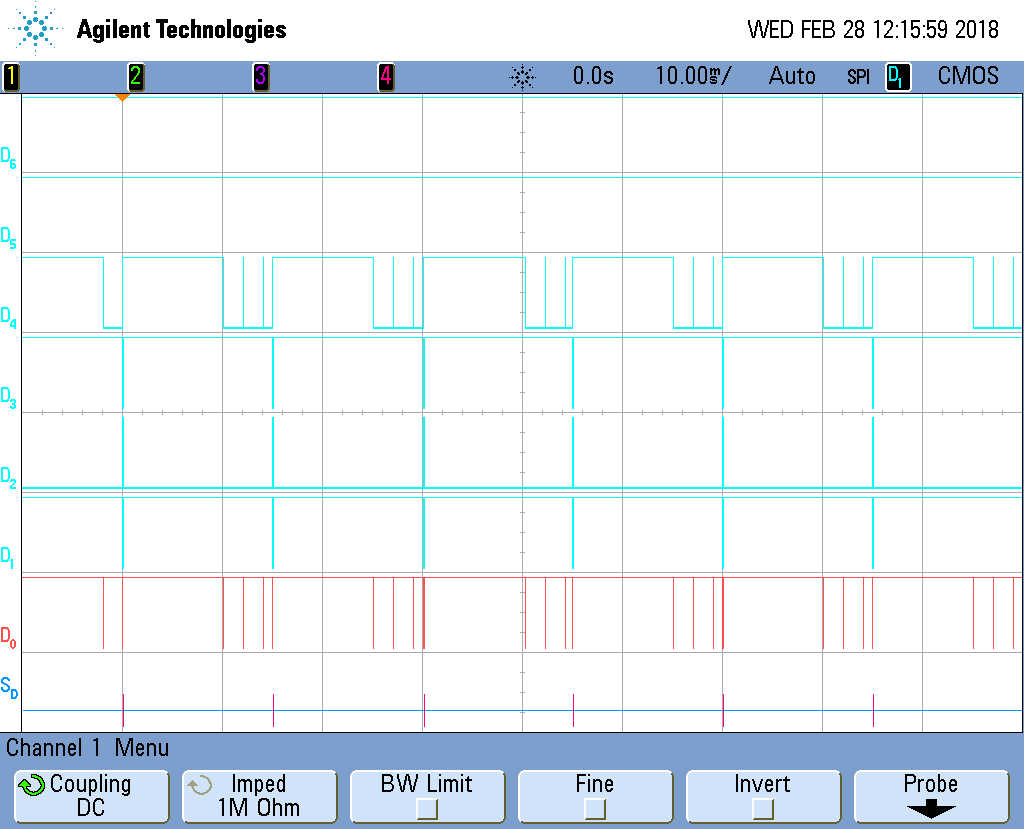

I'm currently working on the project with two ADS1292R daisy-chained, using one internal CLK as the external CLK for the other, both in RDATAC mode with test signal on the input and synchronized by toggling the START pins both with the same signal. When I start data converting, it seems that both devices DRDY signals behave the same way, even if I start communication with only one of them. This issue causes regular data collecting from one device, while the other issuing data only randomly.

Is there anyone experienced with multiple device configuration who would be able and willing to give me any advice or have an idea what could be a problem?

Thank you very much!