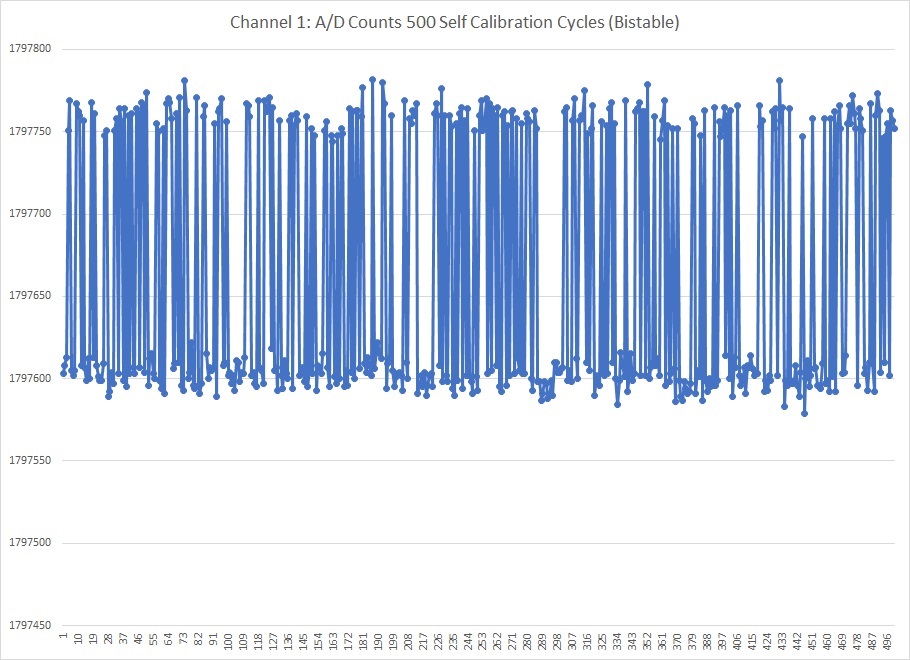

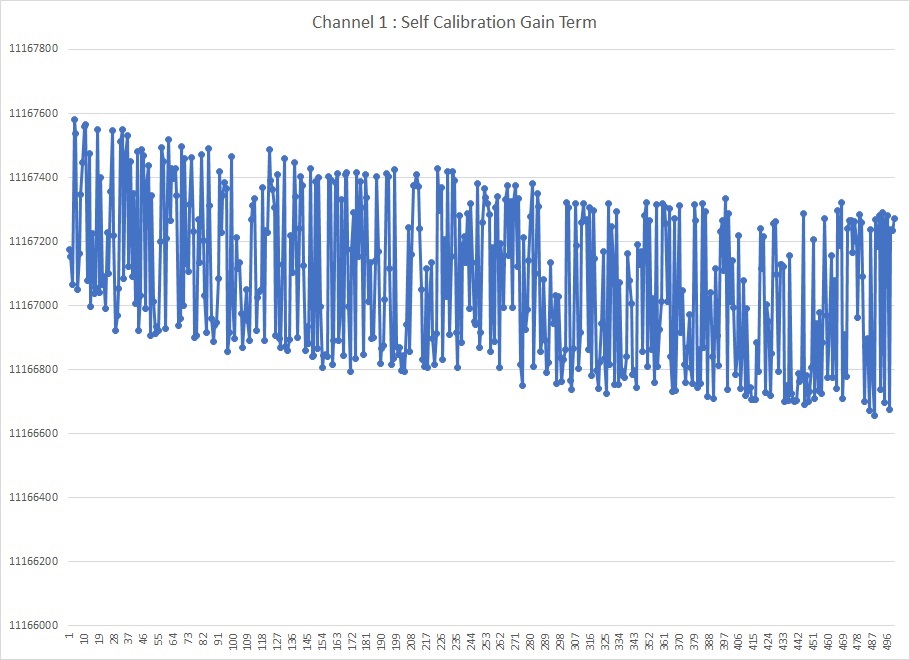

It looks like, possibly, a register is rolling over in the correction algorithm. The Offset and Gain terms generated during the self calibration are on a continum, yet the A/D output is bistable. I either get X as an output or X+150. Never anything in-between. This is persistent until another self calibration is run. I have a lot of parts doing this.

The configuration registers are set to Hex 42085457.

The input is 1.07 V.

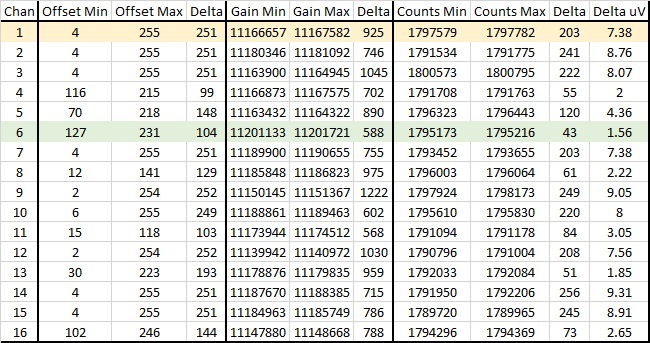

This is one A/D reading for each of 500 self calibration cycles...

These are the corresponding self calibration gain terms...

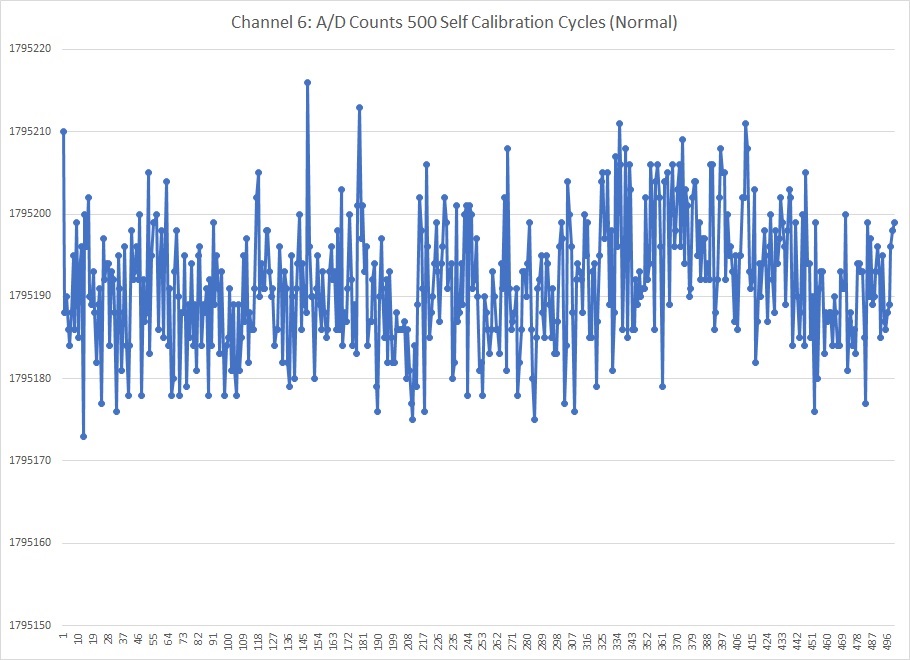

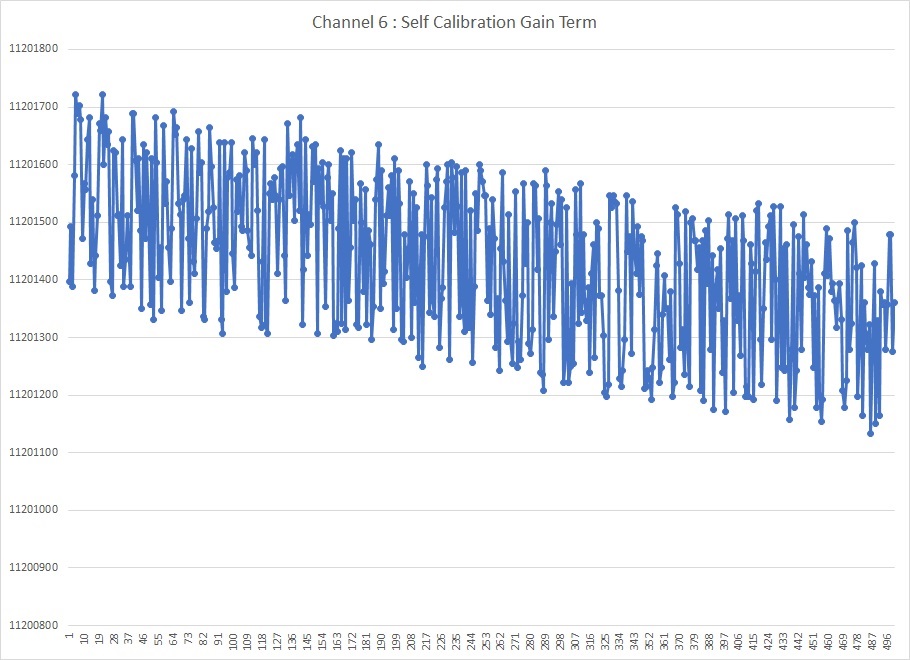

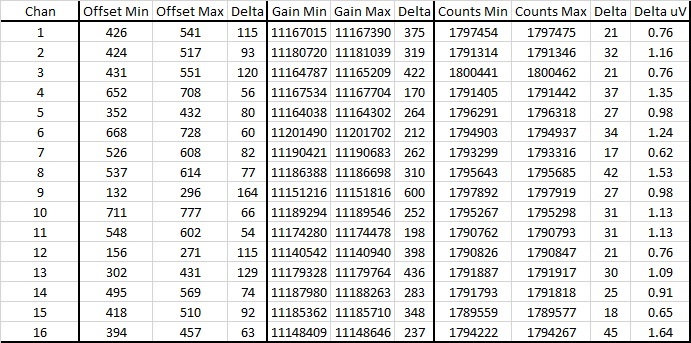

Here is data from a normal part....

These results are very repeatable.

My system noise is generally around 30-40 counts. This was a four hour test, so there is a bit of thermal drift. I am not concerned with that.

Any insights would be appreciated.

Thanks,

Chris