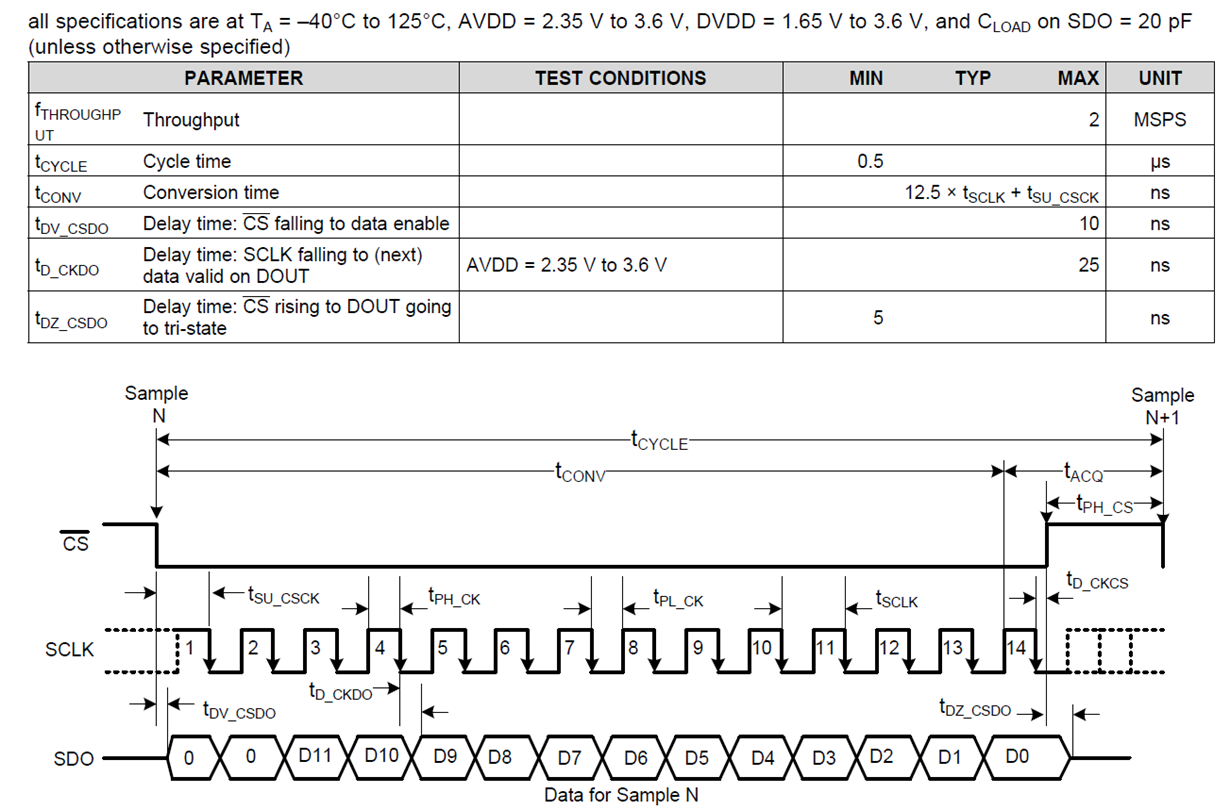

In data sheet it mentions 25ns is the MAX value for data valid delay. It would actually give problems for reading in the data when SPI SCLK speed is higher than 20 MHz (no margin for setup timing and hold timing). Is there a low limit exist? Or for SCLK >20MHz, delay at controller side is required? Thanks!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.