Hi

I have 8 different boards (one DAC8554 on each board). I have done the following test:

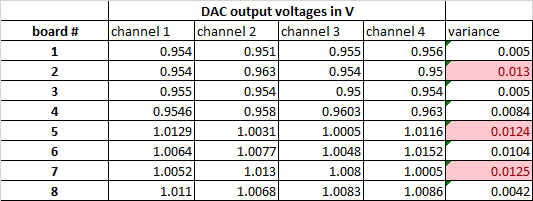

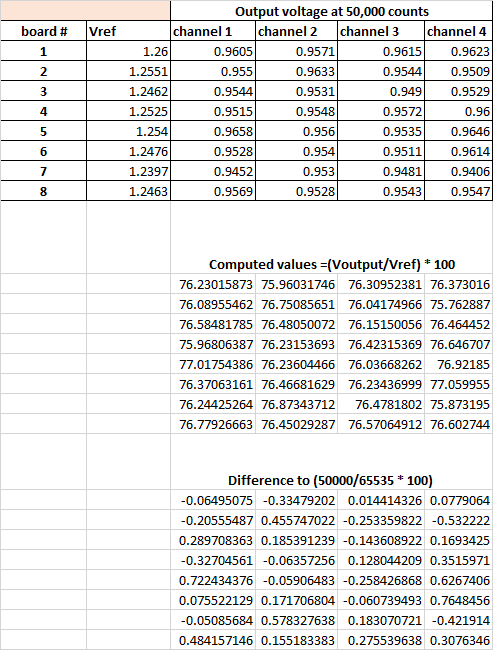

-set all outputs to 50,000 on all 8 boards.

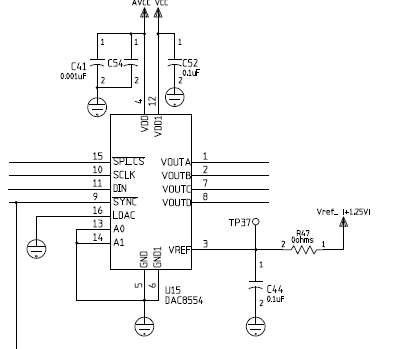

-Vref used is approx 1.25V on all boards (approx because there are board-to-board variations)

Results are attached

According to the DAC8554 datasheet, I have calculated a TUE of 0.971815% of FSR, which is equivalent to 12.1mV if using Vref = 1.25V.

Given this TUE, I would expect the variance between all channels to not exceed the absolute max 12.1mV. However this test shows that 3 out of 8 DACs have their outputs "deviate" upto the marginal values 12 and 13mV...

What am I missing? Is this the way TUE should be interpreted?

Thank you for your help

Isabelle