Other Parts Discussed in Thread: DAC161S997, , DAC8771, DAC8750, DAC8760

Dear sir,madam

Please find the attachment pdf, and let me know is there any changes required in design.

Application.

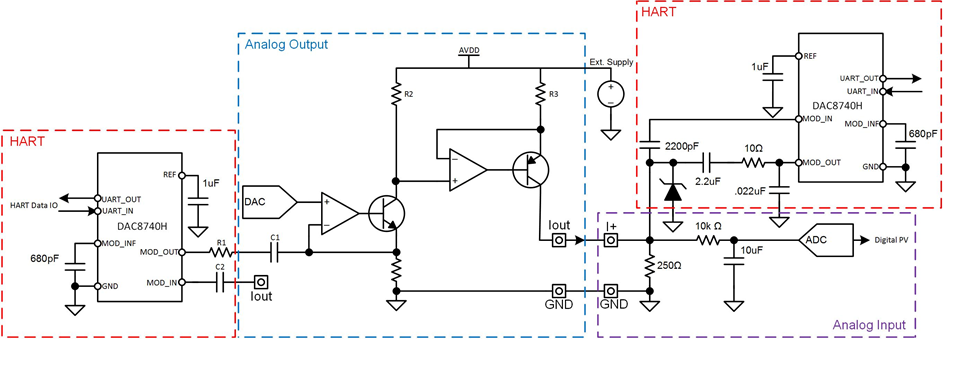

1) we are designing 2-wire loop power 4-20mA output with HART.

2) we are using DAC161s997 to convert digital signal into analog output.

3)We are communicate DAC8740H with DAC161S997, Please checked and let me know is that correct circuit design.TWO WIRE 4-20mA WITH HART.PDF