Hi,

This is a continuation on the thread here (https://e2e.ti.com/support/data_converters/precision_data_converters/f/73/t/696153). Ryan Andrews previously suggested a scheme to test RLD with ADS1299, which I finally got a chance to test out.

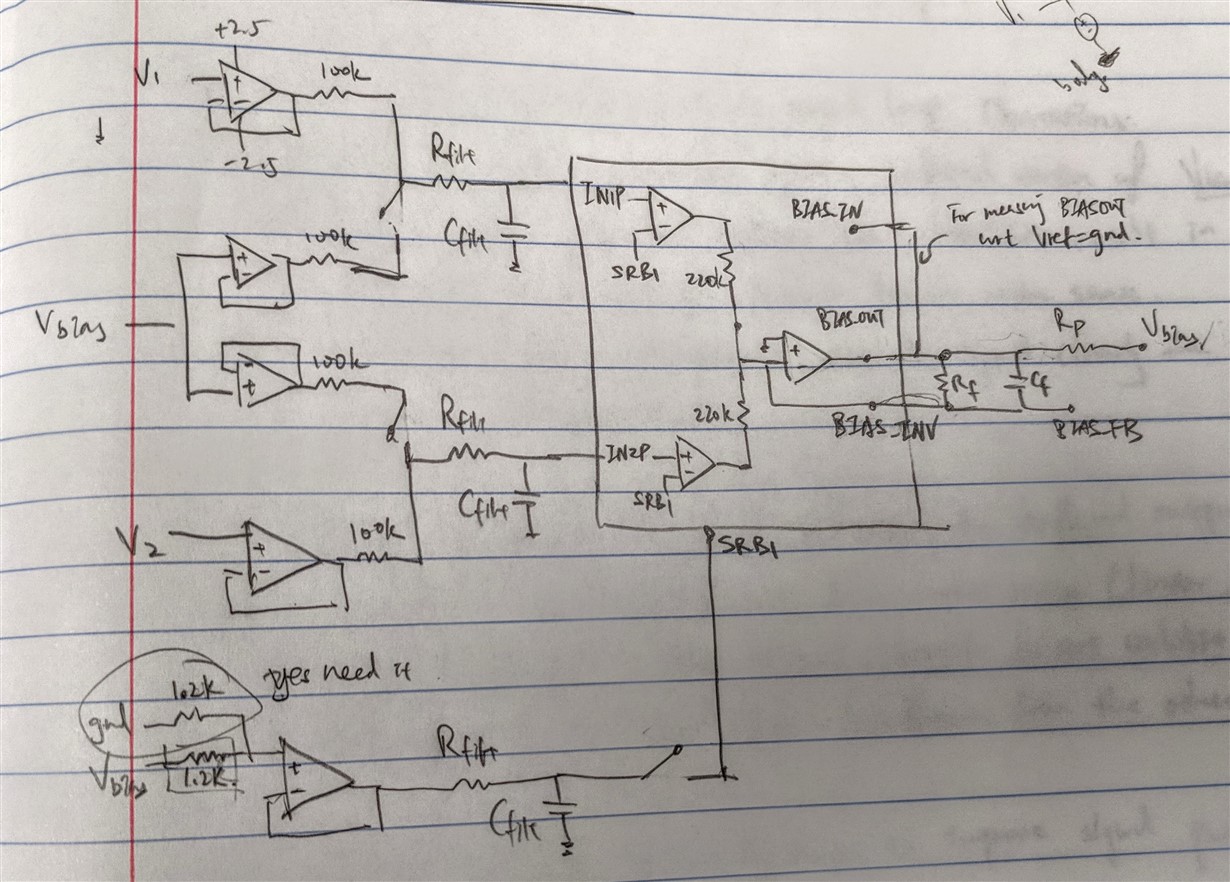

My test results are a bit confusing, I'm hoping to check if what I got is expected. Below is the my final test setup for RLD (same as the last one suggested in the linked thread). The test signals V1 and V2 are square waves generated by a raspberry pi and attenuated by voltage dividers.

The big box represent the ADS1299 chip.

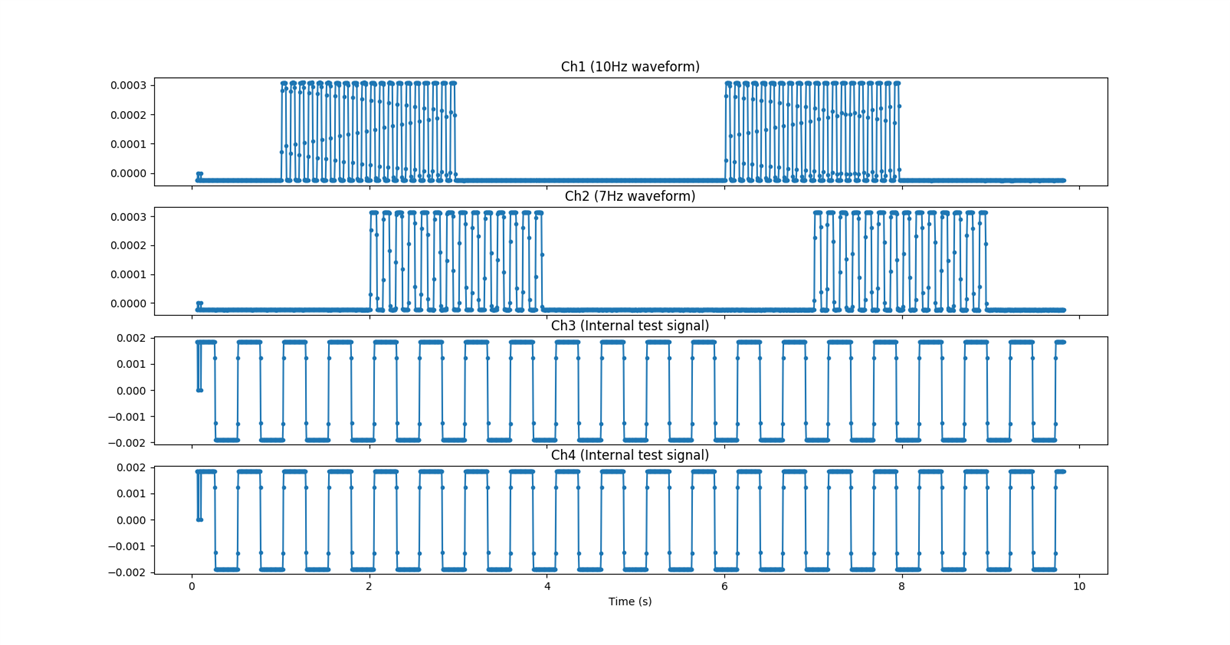

Test 1: The bias amplifier is turned off. V1 and V2 are fed directly to Rfilt, the op-amp summers were not used in this test.

Ground (equal to average of VSSA and VDDA, and V1 and V2 signals are generated with respect to this voltage level) is fed into SRB1 directly. This is my baseline measurement.

Ch1 and Ch2 show clean square waves of 0.3mV as expected (vertical axis is in volts). The temporal delays are as correct. Ch3 and Ch4 are internally generated signals. Everything looks good.

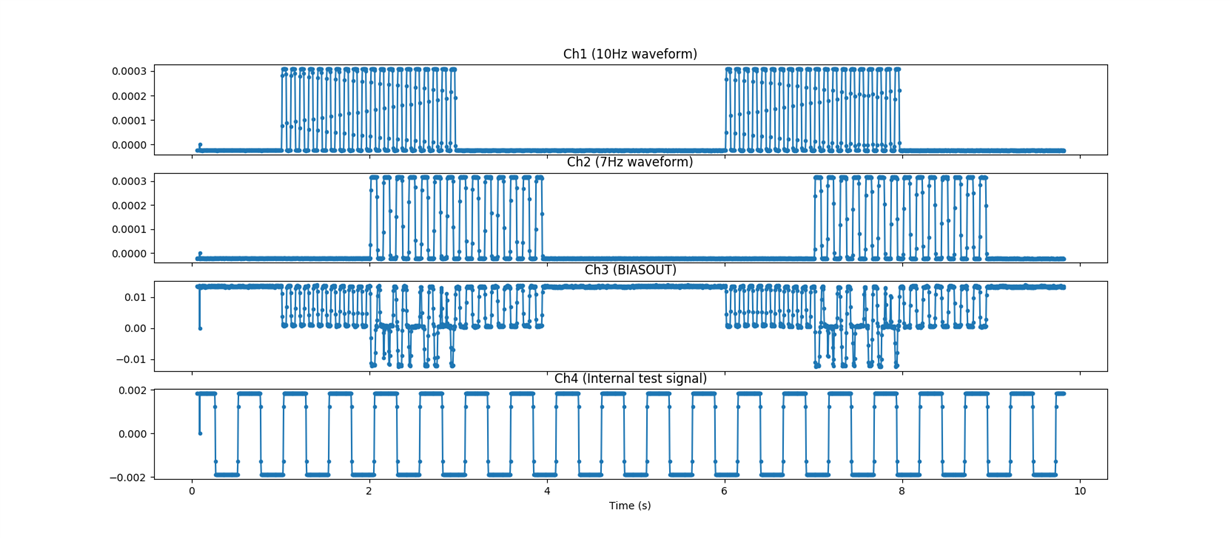

Test 2: Ch1 and Ch2 are as before. Now BIASOUT and BIASIN are connected and routed to IN3P. BIAS_SENSP are configured such that IN1P and IN2P are routed to the bias amplifier to produce averaged common mode, which is applied on BIASOUT pin. Because the feedback loop is open, we see Ch1 and Ch2 signals are unaffected.

Test 3: Here we close the RLD feedback loop. Buffered V1 and V2 are summed with buffered version of Vbias before reaching IN1P and IN2P. Buffered Vbias instead of ground is fed into SRB1. The resulting signals are shown below. Ch1 and Ch2 are now severely attenuated and the square waves are about 20uV peak-to-peak. However, the BIASOUT measured on Ch3 is perfectly flat.

This doesn't make too much sense..

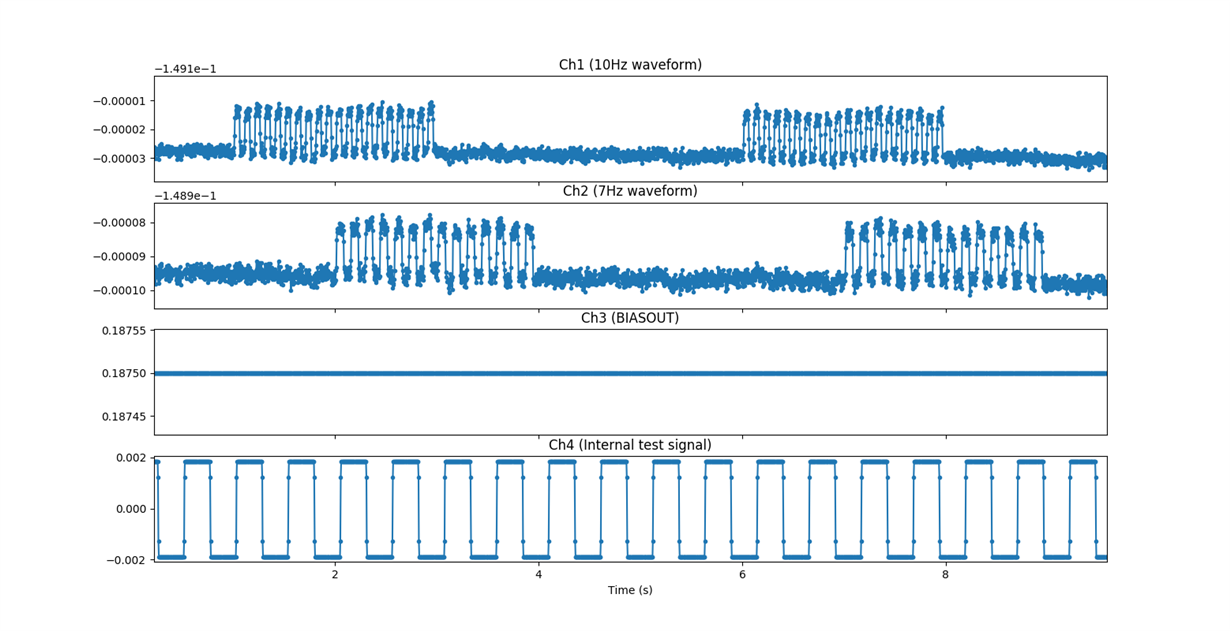

Test 4: In the final test, Vbias and ground is summed together, and the summer's output is applied to SRB1. The resulting Ch1 and Ch2 are noisier and shows some interference from the other channel.

However, the amplitude of Ch1 and Ch2 are not attenuated as much (0.2mV peak-to-peak, which is more reasonable). Ch3 shows BIASOUT that looks like the average of Ch1 and Ch2.

So my questions are: While test 3 shows cleaner measured signals, why would BIASOUT flat in test 3? Is this expected?

I think test 4 is a closer simulation of what happens during actual EEG measurement, i.e. the potential on the ground electrode is affected by the bias drive. But in this case, what can be done to minimize the inter-channel interference due to the common-mode extraction by averaging? I think changing the Vbias+V1 or Vbias+V2 summer resistors can tune this behavior, but this is hardly controllable during actual EEG usage.