Other Parts Discussed in Thread: ADS1248

I am Japanese. Explanation may be insufficient.

Operation is done by setting the 23rd pin (START) of ADS1148 to HI.

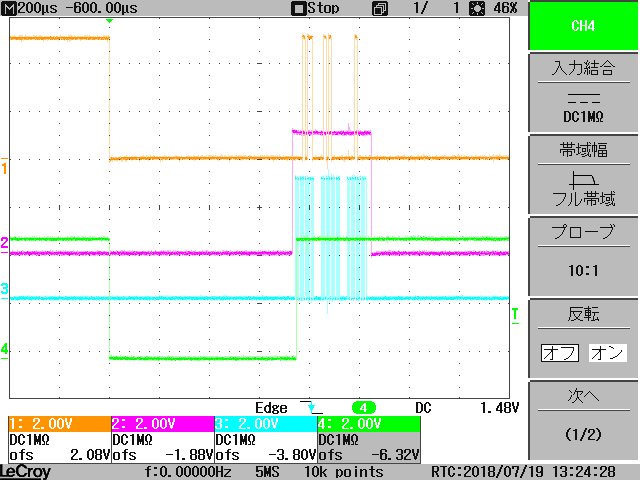

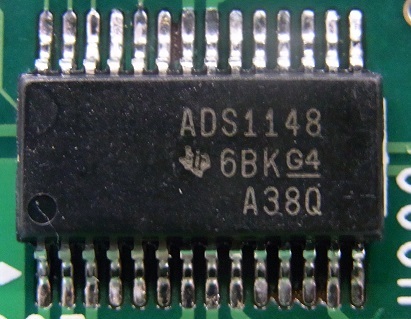

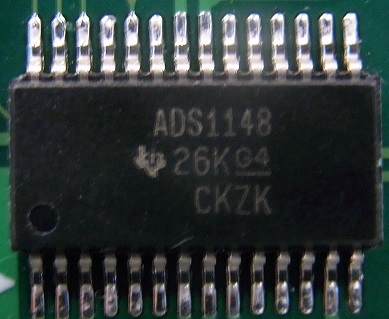

The operation differs when comparing the two ADS1148.

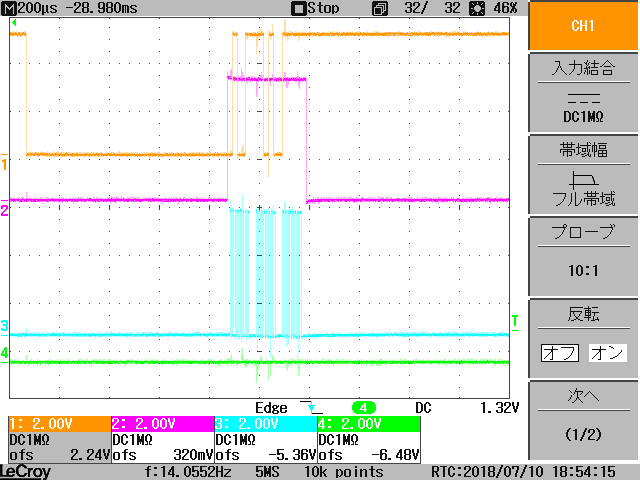

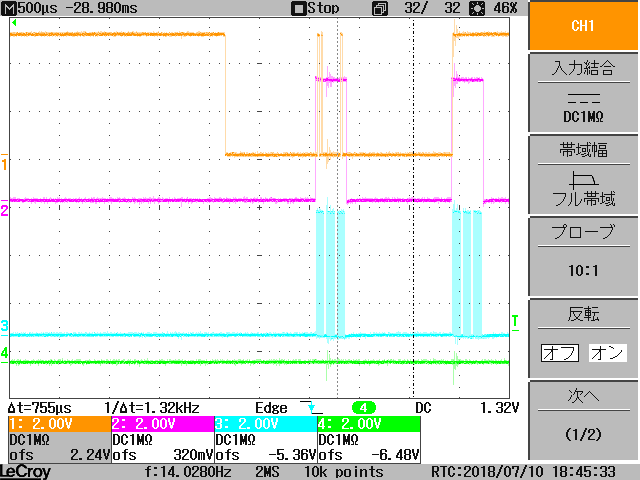

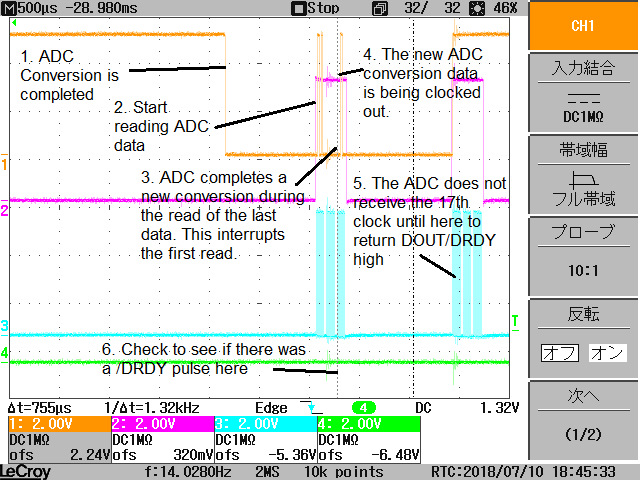

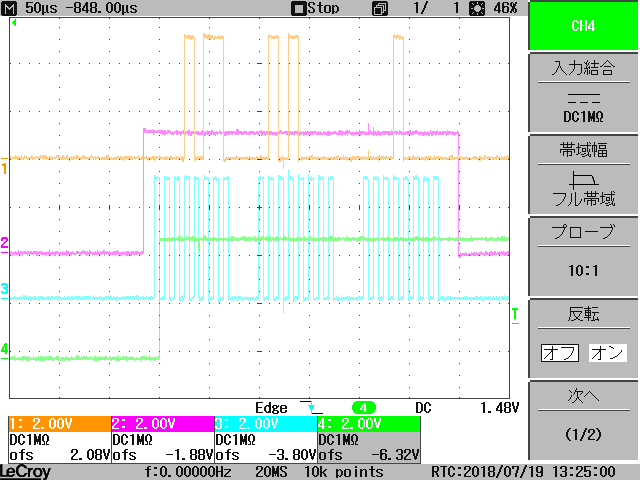

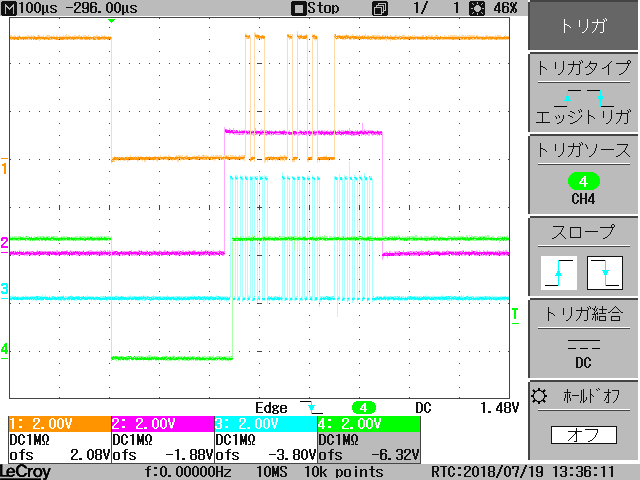

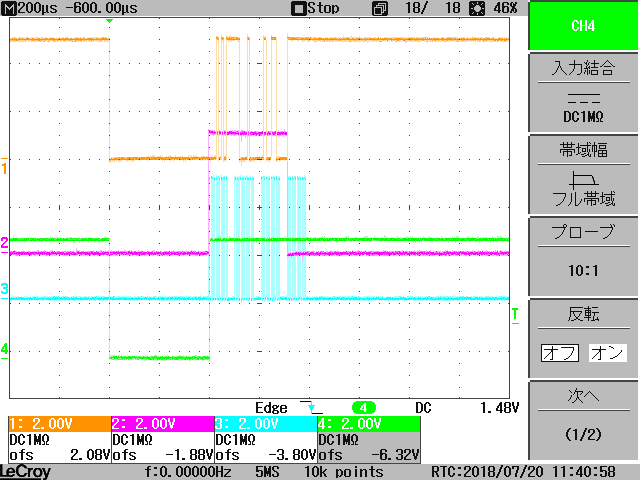

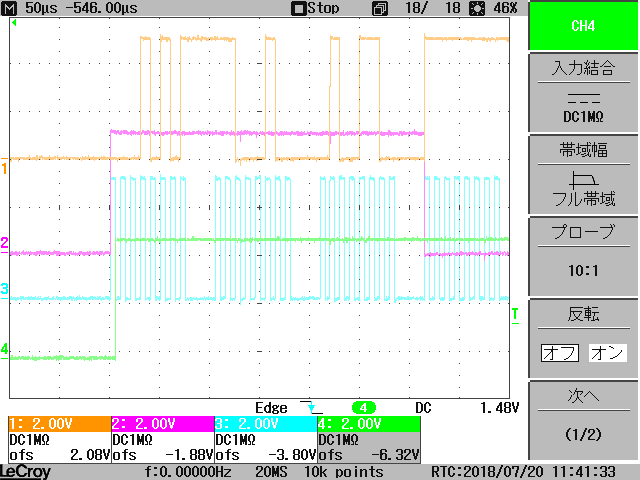

CH1(Yellow): MISO(DOUT/DRDY#) , CH2(RED):MOSI(DI)

CH3(BLUE):CLK, CH4(GREEN):CS

DRDY # is HIGH with the next NOP instruction after data output

DRDY # does not go HIGH with the next NOP instruction after outputting data.

DRDY # becomes HIGH with two NOP instructions.

Movement is different though it is the same model number

Which is the correct behavior?

After outputting data, DRDY # goes high at the next rising edge (CLK) and it was written in the data sheet.

It seems there are 24 bit data output even though it is a 16 bit product.

Why is DRDY # not going High at the next rise (CLK) after data output