Hi,

We did a design with ADS1234 to measure four load cells.

I'm using the SPI from my MCU to read the data when the pin DRDY/DOUT goes to low level.

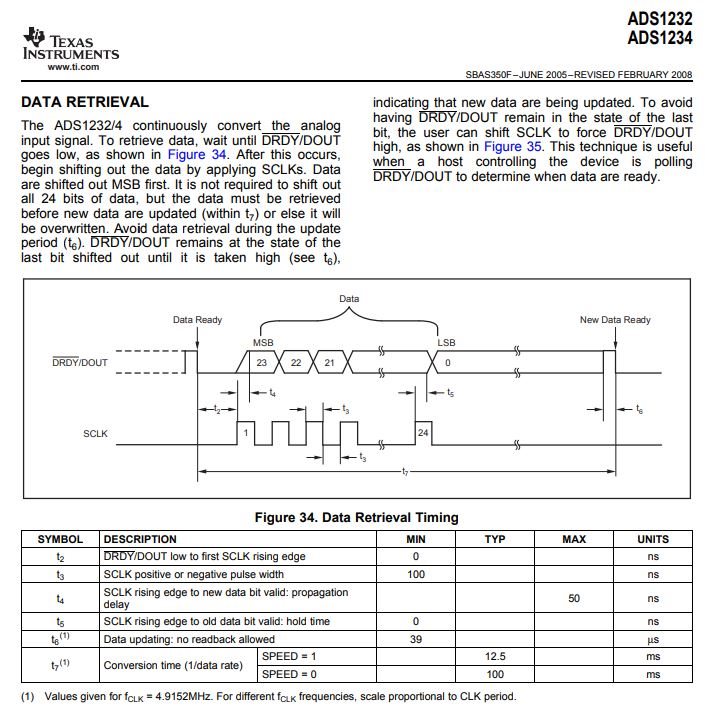

Respecting the datasheet, on section of DATA RETRIEVEL, we set SPI speed fast enough to get a negative or positive clock of 50ns.

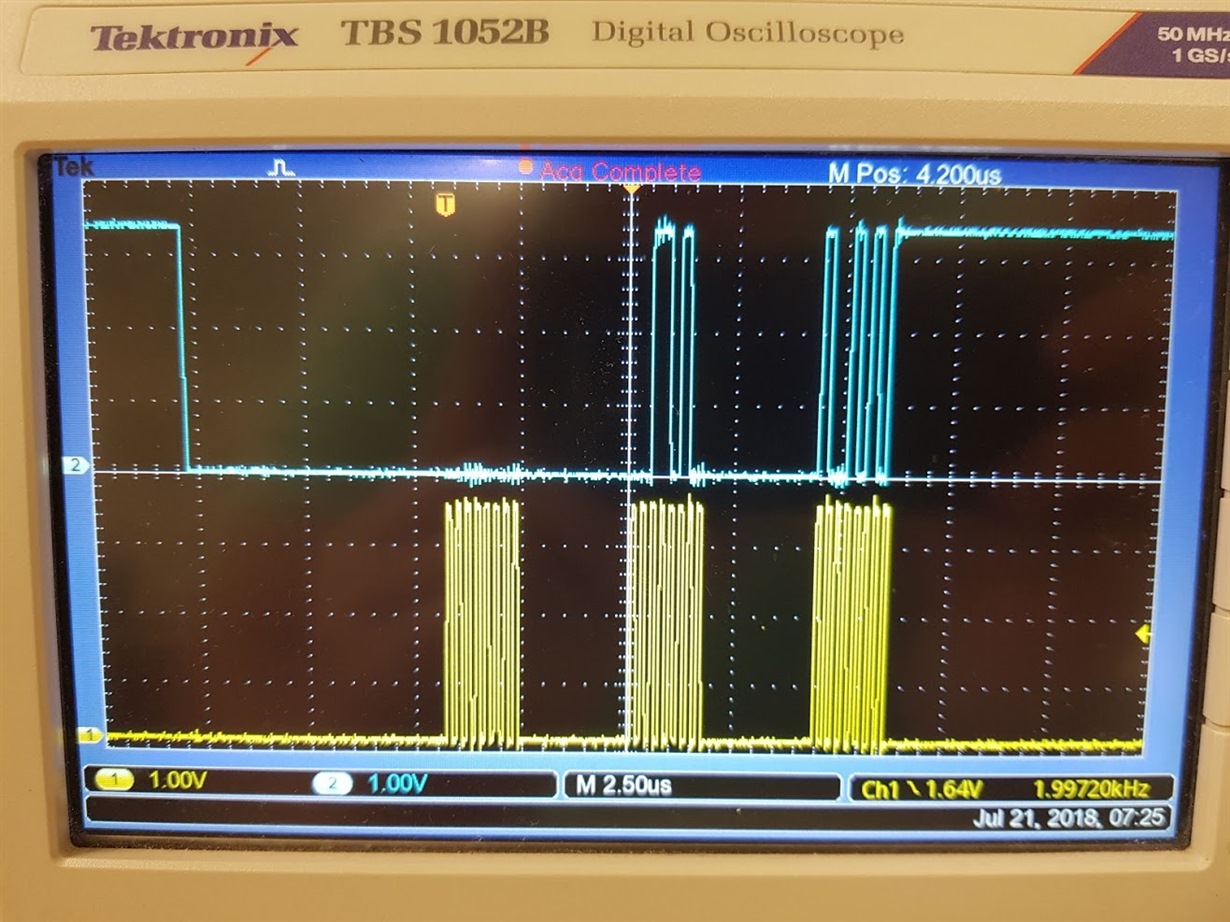

Using the oscilloscope we could see the 50ns of the clock signal, but when I read the data, the clock signal is not constant. The image below show the behavior of my MCU.

This behaivor of the SPI could generate a problem to the ADS1234?

The clock signal needs to be constant? The gap from each clock is 2.70us.

To read all the 24 bits, the SPI is spending @ 16.25us counting after DRDY/DOUT going to low level.

According to the datasheet, after the signal of DRDY/DOUT goes to low, I have 100ms to read all the 24bits.

My speed is set to 10SPS.

I would like to double check this behavior of my clock signal and be sure this will not be a problem for us.

Thank you!!