Other Parts Discussed in Thread: AMC1210

Hi everybody,

I'm using AMC1304L25 to measure DC+AC voltage, up to approx. 250V. Thus using large voltage resistor divider.

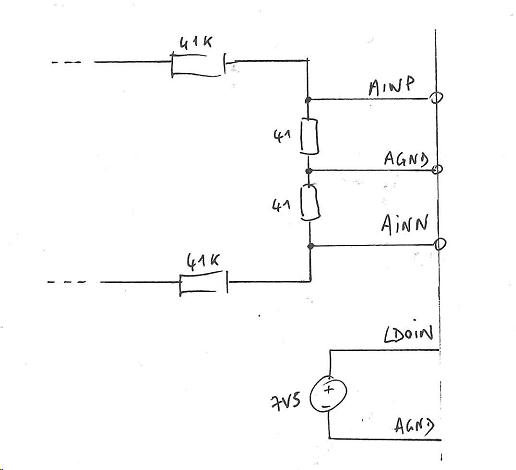

I designed a fully symetrical input stage to cope with issue described in section 9.2.2 of the datasheet.

I mean the sensing resistor is splitted in two and the middle point connected to AGND. This is slightly different from figure 56 of the datasheet.

But we are getting approximately -2.2% of error (measured at different voltage levels). Apparently a gain error.

Is it the right thing to do ?

thanks and regards,

Alain