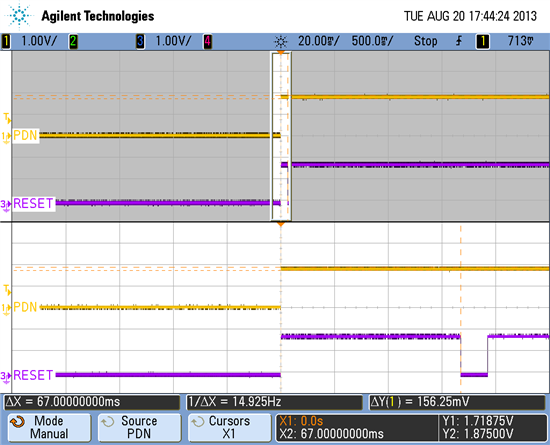

I am using TVP5151 connected to OMAP3 processor. The crystal is running at 27 MHz as specified. The SCLK output signal is 1.025 MHz rather than 27 MHz expected. The signal has been traced with an oscilloscope and shows a nice square wave at 1.025 MHz. What could be causing this operation?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.