Hi All,

We are using THS8200 IC for converting LCD parallel signal to VGA on phyBOARD-WEGA-AM335x(SOC AM3359).

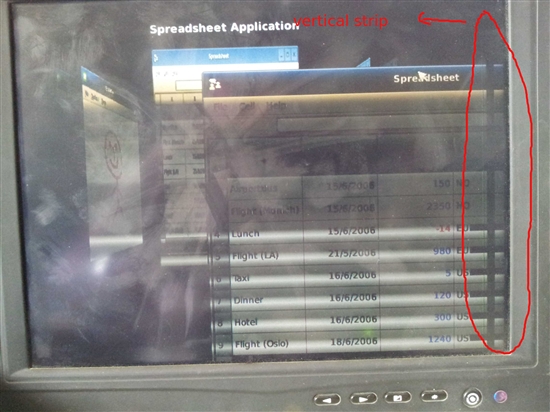

On VGA monitor we are getting on vertical stripe.

If i moves the QT application to that area, shadow is coming on the VGA monitor.

Please find attached jpg for problem.

I am using below XGA resolution.

XGA 1024 x 768 @ 60 Hz pixel clock 65.0 MHz

Horizontal Timing (pixels) Vertical Timing (lines)

Visible area 1024 768

Front porch 24 3

Sync pulse 136 6

Back porch 160 29

Whole line/frame 1344 806

Bellow are the register values of THS8200 IC.

*************************************************************************

DATASET_NAME,"DMT ID: 10h, 1024x768 @ 60Hz, 48.363kHz, 65.000MHz, HS/VS -/-, RGB 444 DS>VGA, THS8200"

//THS8200

INCLUDE,THS8200_RGB_444_DS_to_VGA_common.inc

register value

WR_REG,THS8200,0x01, 0x34, 0x05 // dtg1_total_pixel_msb

WR_REG,THS8200,0x01, 0x35, 0x40 // dtg1_total_pixel_lsb

WR_REG,THS8200,0x01, 0x39, 0x33 // dtg1_frame_field_msb

WR_REG,THS8200,0x01, 0x3A, 0x26 // dtg1_frame_size_lsb

WR_REG,THS8200,0x01, 0x3B, 0x26 // dtg1_field_size_lsb

WR_REG,THS8200,0x01, 0x70, 0x88 // dtg2_hlength_lsb

WR_REG,THS8200,0x01, 0x73, 0x07 // dtg2_vlength_lsb

WR_REG,THS8200,0x01, 0x82, 0x40 // dtg2_cntl, RGB mode, discrete syncs

regards,

syed