Team,

Customer found issue which is related with PWDN signal timing. Please refer to the below for more details, and let us know your answer.

- Device: TPV7002

- Issue description

-

Initial status of PWDN signal is high. Then, PWDN signal (High to Low) was applied about 4.4msec later than RESET signal (Low to High) during board power-on procedure. Refer to the screenshot in below.

-

With this timing sequence between PWDN and RESET signals, the TPV7002 device was not working properly.

Questions/Requests

-

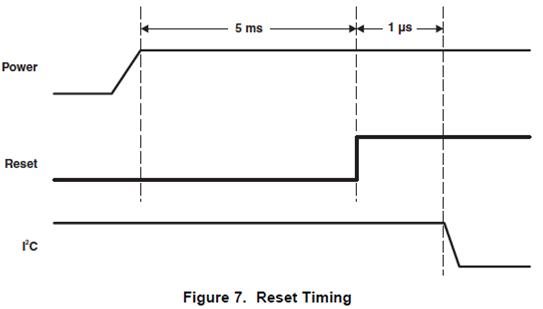

Couldn’t find timing requirements between PWDN and RESET signals from the datasheet. Only below timing diagram is available. Please provide timing requirements between PWDN and RESET signals.

-

In my understanding, this power-down mode turns off all device blocks during PWDN signal is High status. So we should perform RESET (Device initialization) procedure after this mode. Is it correct?

-

We found that TPV7002 supports power-down mode thru register configuration as below. What should be done after this power-down mode? Do we require RESET (Device initialization) procedure again after this mode?

Thank you in advance!