Hi,

I'm migrating a project (which works fine) to a new project, because I was unhappy with the structure and I needed to add new features.

All I've done is copy-paste code from the old project to the new project, but in different files.

Every now and then I checked whether the code compiled and would run.

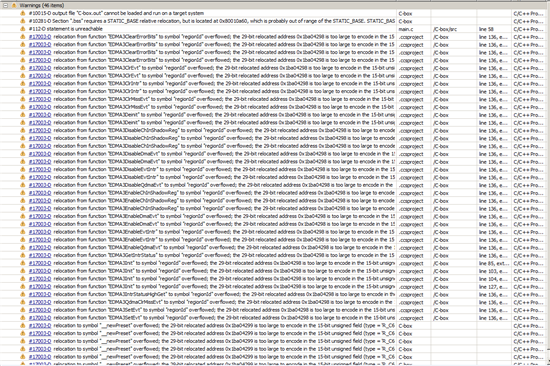

After the last (and biggest) code copy, I get the errors as shown in the attachment.

The problems are reported in places which worked before (i.e. they were not copied in the last action) or they are reported in TI's code.

I've also added my linker command script, but as it's the same as the working project, I doubt the problem is in there.

I've no idea where to start looking for this problem, so how do I tackle this?

Thanks in advance.

Kind regards,

Remco Poelstra

/****************************************************************************/

/* C6748.cmd */

/* Copyright (c) 2010 Texas Instruments Incorporated */

/* Author: Rafael de Souza */

/* */

/* Description: This file is a sample linker command file that can be */

/* used for linking programs built with the C compiler and */

/* running the resulting .out file on a C6748 */

/* device. Use it as a guideline. You will want to */

/* change the memory layout to match your specific C6xxx */

/* target system. You may want to change the allocation */

/* scheme according to the size of your program. */

/* */

/****************************************************************************/

MEMORY

{

DSPL2ROM o = 0x00700000 l = 0x00100000 /* 1MB L2 Internal ROM */

DSPL2RAM o = 0x00800000 l = 0x00040000 /* 256kB L2 Internal RAM */

DSPL1PRAM o = 0x00E00000 l = 0x00008000 /* 32kB L1 Internal Program RAM */

DSPL1DRAM o = 0x00F00000 l = 0x00008000 /* 32kB L1 Internal Data RAM */

SHDSPL2ROM o = 0x11700000 l = 0x00100000 /* 1MB L2 Shared Internal ROM */

SHDSPL2RAM o = 0x11800000 l = 0x00040000 /* 256kB L2 Shared Internal RAM */

SHDSPL1PRAM o = 0x11E00000 l = 0x00008000 /* 32kB L1 Shared Internal Program RAM */

SHDSPL1DRAM o = 0x11F00000 l = 0x00006000 /* 32kB L1 Shared Internal Data RAM (24kB)*/

EMIFACS0 o = 0x40000000 l = 0x20000000 /* 512MB SDRAM Data (CS0) */

EMIFACS2 o = 0x60000000 l = 0x02000000 /* 32MB Async Data (CS2) */

EMIFACS3 o = 0x62000000 l = 0x02000000 /* 32MB Async Data (CS3) */

EMIFACS4 o = 0x64000000 l = 0x02000000 /* 32MB Async Data (CS4) */

EMIFACS5 o = 0x66000000 l = 0x02000000 /* 32MB Async Data (CS5) */

SHRAM o = 0x80000000 l = 0x00020000 /* 128kB Shared RAM */

DDR2 o = 0xC0000000 l = 0x20000000 /* 512MB DDR2 Data */

}

SECTIONS

{

.text > SHRAM

.stack > SHRAM

.bss > SHRAM

.cio > SHRAM

.const > SHRAM

.data > SHRAM

.switch > SHRAM

.sysmem > SHRAM

.far > SHRAM

.args > SHRAM

.ppinfo > SHRAM

.ppdata > SHRAM

.data_sh1ram > SHDSPL1DRAM

.data_sh2ram > SHDSPL2RAM

.data_ddr > DDR2

/* COFF sections */

.pinit > SHRAM

.cinit > SHRAM

/* EABI sections */

.binit > SHRAM

.init_array > SHRAM

.neardata > SHRAM

.fardata > SHRAM

.rodata > SHRAM

.c6xabi.exidx > SHRAM

.c6xabi.extab > SHRAM

}