Hi all,

I have got a relatively frustrating problem I am hesitating trying to debug, I have a single project that when compiled functions as expected, but when increasing the length of a string literal (any string literal) I can cause various erroneous behavior (static variables being set to unreasonable values for instance) or an entire program hang. By shortening various other strings I can then keep the previously problematic long string unchanged. I am suspecting this is due to a linking issue, but I have not been able to find anything that is incorrect.

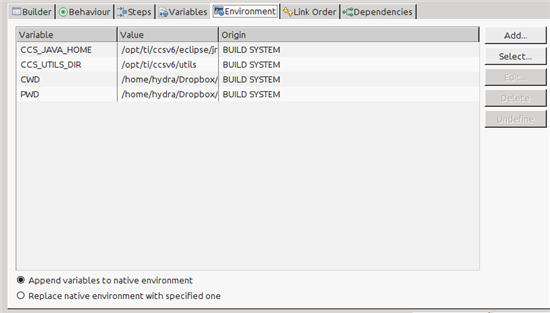

I am using compiler 6.2.8 in CCS 6.0.1.00040 on a TMS320F28069MPNT.

My memory map setup is relatively standard and shown here;

I have verified that my stack does not overflow (I have some 3kWord reserved and I have seen a worst-case utilization of around 500 words), furthermore I have verified that the .econst section is loaded into memory and that resonable strings/values can be found in the range specified by my .map file.

Is there any problem with placing .text, .ebss, .econst, and .esysmem in the same memory region? Is there any problem with allocating all of L2 through L8 as one contiguous block, or are there some obscure page boundaries there? (neither the CLA nor secure-zone is enabled).

Any help would be greatly appreciated!