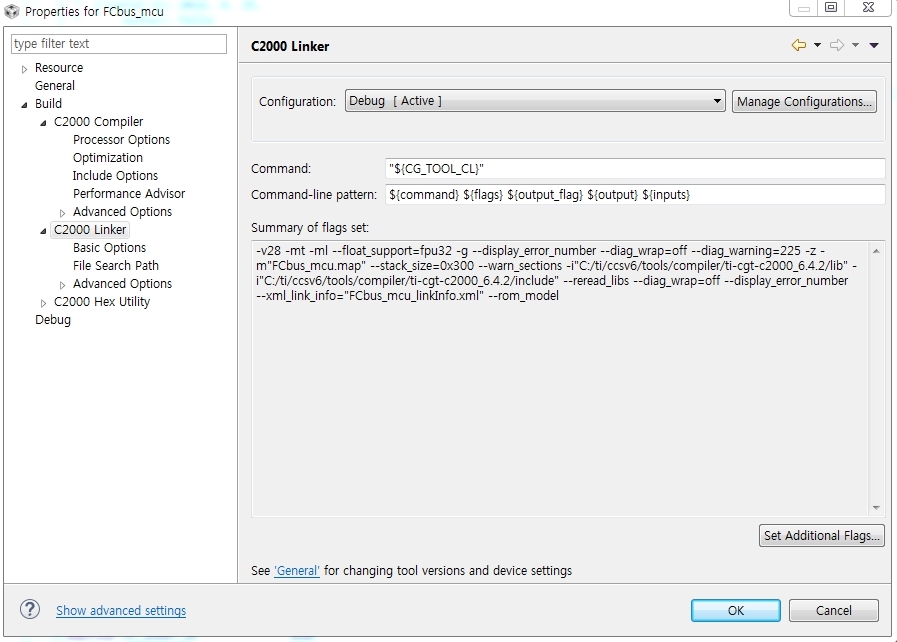

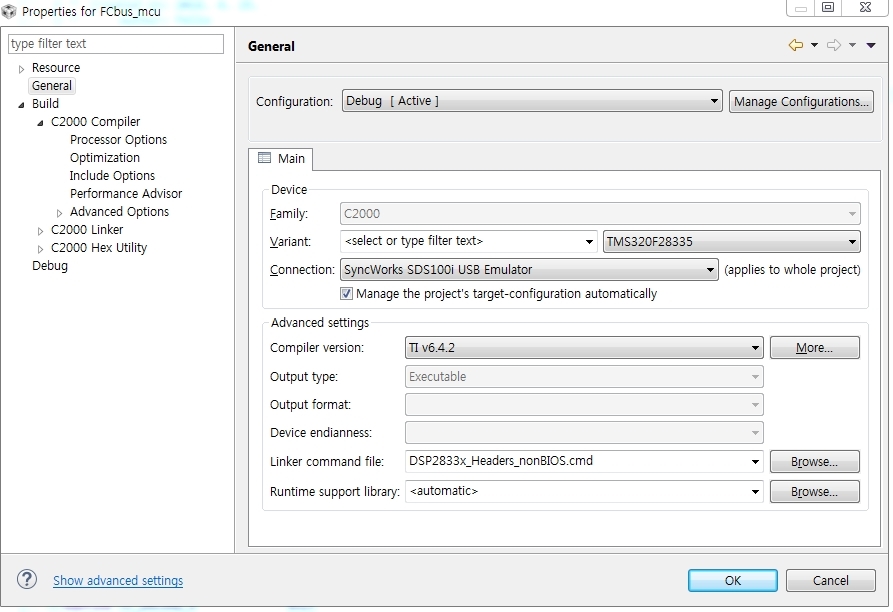

Tool/software: TI C/C++ Compiler

HI.

I'm developing ECU using 28335.

Recently, phenomenon has occurred the ECU died after the code is entered. so i broken four ECUs.....

While searching for the cause, I found that the order of the newly added CAN communication MailBox initialization code was intertwined.

The mailbox initialization code (ID, Direction, etc ...) was declared separately at the bottom of the initialization function instead of the previously set order.

So I modified the initialization code that was declared at the bottom to match the order in which other existing MailBoxes are declared, so the ECU die phenomenon is gone.

Could the initialization code sequence cause a critical problem inside the ECU?

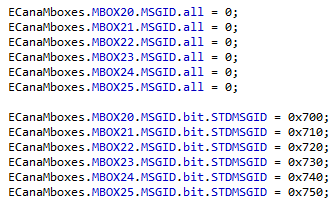

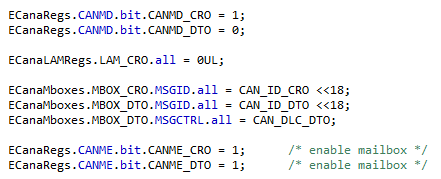

The attached picture is the initialization code of the newly added MailBox and the existing initialization code before the problem was solved.

The problem was solved when I joined the things that were separated from each other like that..