hi,

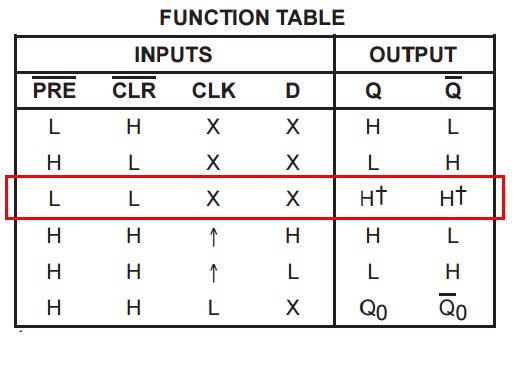

I am simulating an schematic with SN74HCT74 flip-flop. I am only using Clear, Preset and Output pins. I want to simulate the situation that I mark in red color in the following image:

The problem is that I don't see a high value in the output. I attach the simulation file in case it helsp.

Thanks,

Marina.