Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

Hi,

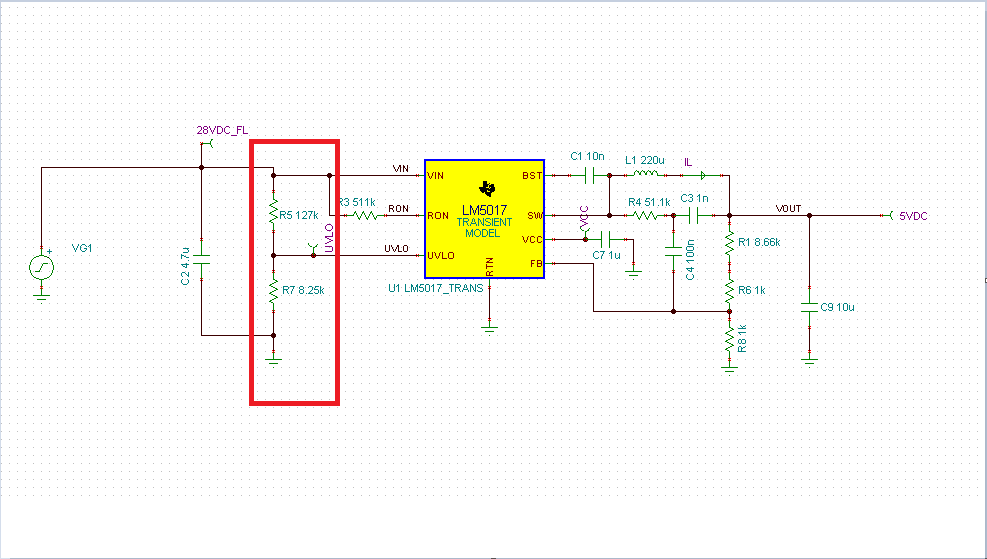

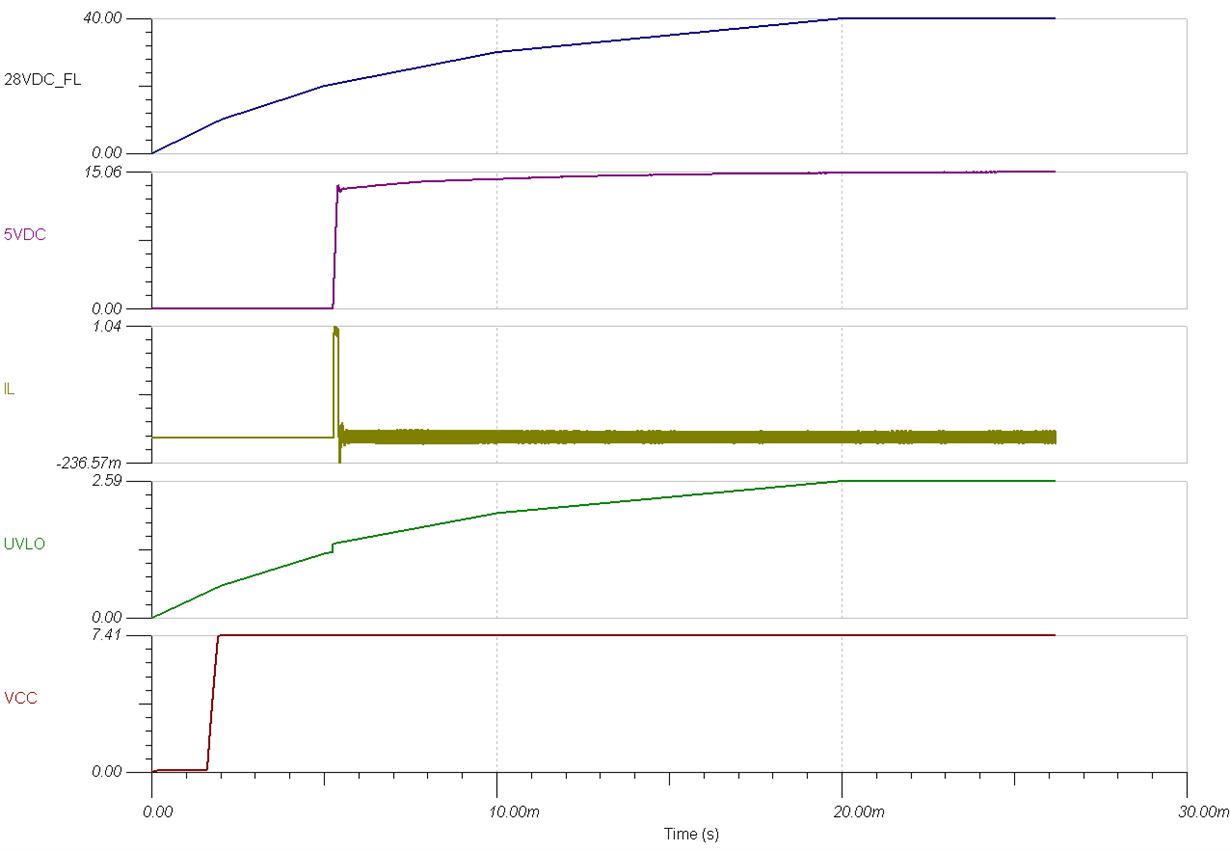

I am using LM5017 switching regulator and doing transient analysis on it.

Please refer the attached circuit.

Problem:

when the input voltage exceeds ~29.5V, tool is throwing a convergence error.

conditions are:

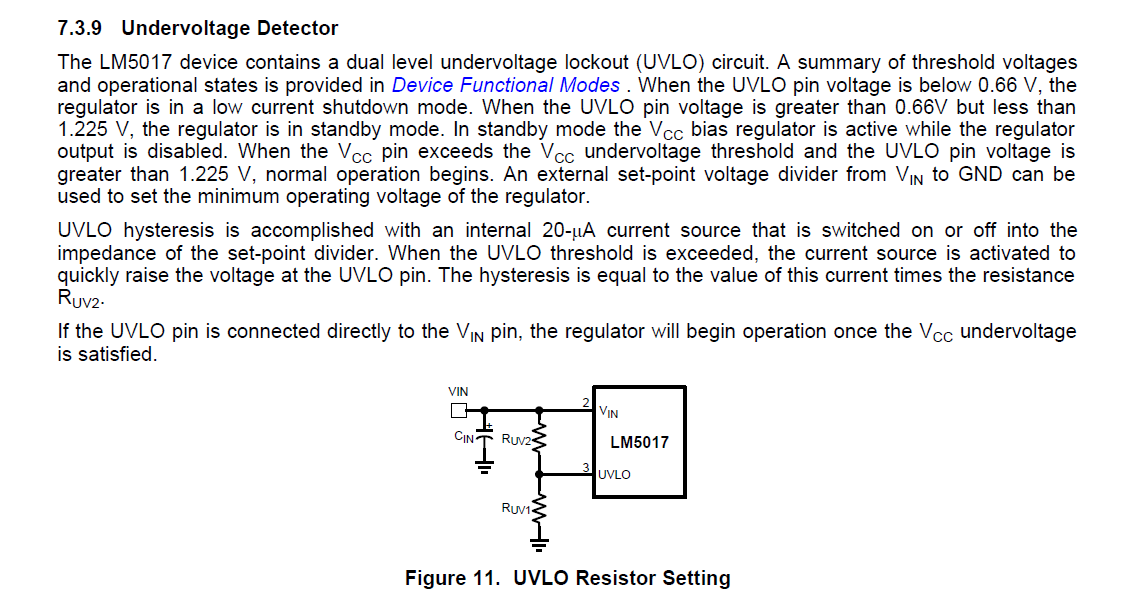

RUV2 5.11E+04 ohm

RUV1 1.00E+04 ohm

Vout 28 V

UVLO pin 4.58 V

and I_Hys 2.00E-05 A {Vin(Hys) = I_Hys * RUV2}

Vin (Hys) 1.02 V

V_IN(UVLO, rising) = 1.225V * [(RUV2/RUV1) +1] = 7.48475 V

Please help me to understand the role of Vin(Hys) and V_IN (UVLO, rising) voltages and

and why is convergence error ocurring the moment UVLO pin voltage is reaching ~5V.

Sunney