Other Parts Discussed in Thread: TINA-TI,

Tool/software: TINA-TI or Spice Models

I would need an AC model for the LMZ21700 in order to check the total impedance of the power delivery network in a digital system.

My concerns are the possible resonances between capacitors and the switcher output in the upper part of the bandwidth.

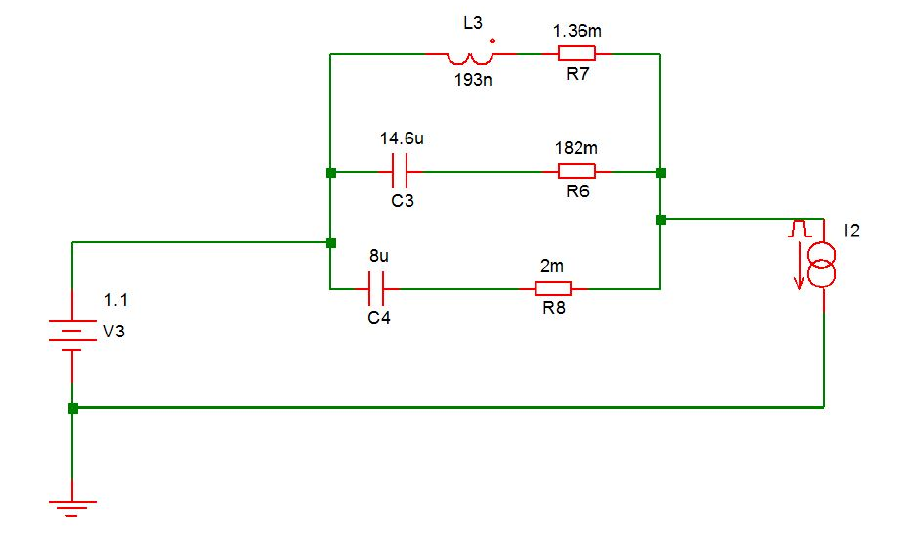

As an AC model is not available, I setup a simulation with the LMZ21700 transient model (set for 1.2V output) and:

- as output capacitor a 200 uF with 0.3 ohm ESR

- as load, the foreseen DC load (0.2A) and a strong AC component (0.2 A pkpk)

then I measured the resulting ripple at frequencies of 25, 50, 100, 200, 400 and 800 kHz.

I gained a fitting polynomial that gives a good approximation of the SMPS impedance: Z(w) = 0.018 - 2E-9 w + 1.8E-14 w^2 (w is the angular frquency 2*pi*f).

A voltage dependent current source in Spice with that frequency function "G1 0 N001 N001 0 Laplace=-1/(0.018-2E-9*s+1.8E-14*s^2" seems to behave similar to the transient model.

Do you rate this method as reliable or can you advice some different way to go ?

Thanks in advance.