A Webench design for a 9.5-16.0v input to 5.0v output @ 8A regulator using the TPS53513 suggests MLCC cap parts that have terrible DC bias problems. The 47uF input caps (TDK C3216X5R1E476M160AC) under 12V DC bias each have <6uF capacitance! The 47uF output caps (Murata GRM31CR61A476KE15L) under 5V DC bias each have only 20uF capacitance (15uF at -40/+85C). Note that these are from the manufacturer's part-specific plots/tools at low (<0.1V) AC ripple voltage, which is what I expect to be the case for this design. It is almost meaningless to list specific part numbers that have such poor correlations (at their operating points) to their nominal capacitance values.

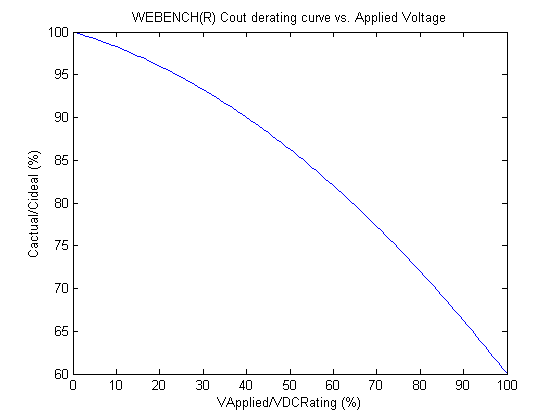

I read in another post that Webench applies a generic derating curve to [only] the output MLCC caps, but upon checking a number of [Murata] caps of various rated voltages, dielectrics, and physical sizes [using their excellent SimSurfing tool], it is apparent that a generic correction is not useful, especially based on rated voltage. The Murata tool showed that the biggest dependency is actually on capacitor size (bigger package volume is better). Even knowing this, the DC bias can have a remarkable effect on the temperature characteristic, often changing the basic datasheet curve dramatically and non-intuitively, so the combined effects are hard to anticipate. I suspect this applies to other manufacturers' parts too. This makes for a tedious task when trying to find suitable caps, especially if trying to minimize size and cost.

Getting back to the TI issue here, can you tell me whether Webench displays MLCC cap values that are theoretical (i.e. ideal component), or does it attempt to select values or part numbers that are intended to simply be used as listed? How would I know which are which? For example, does Webench indeed apply the derating curve mentioned in the post I referred to, and only to output caps?

Thanks in advance for your reply.