Other Parts Discussed in Thread: DLPC900

Hi

Refer to the 6500EVM design. I tried to design a 6500FYE system.

Now I have a fatal problem,in my design, the gray scale of the DMD display is very weak. the DMD chip is good because it works fine on the 6500EVM(same DMD chip).

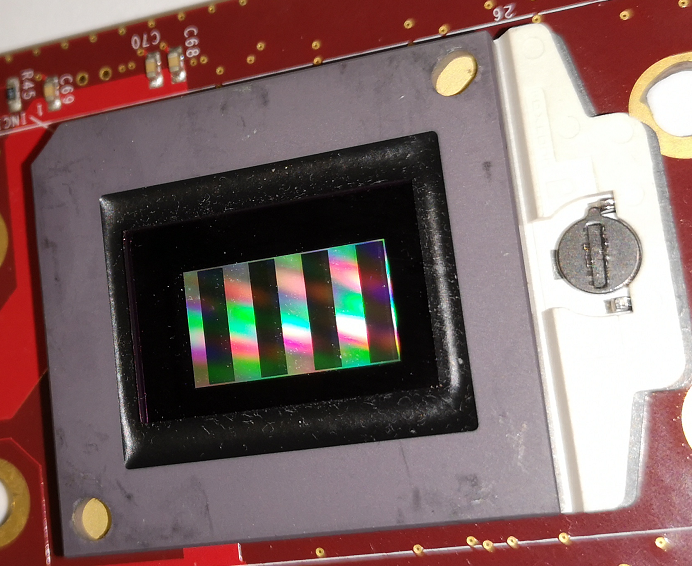

On 6500EVM is works fine, every picture can be seen very clearly,You can easily find a clear viewing angle:

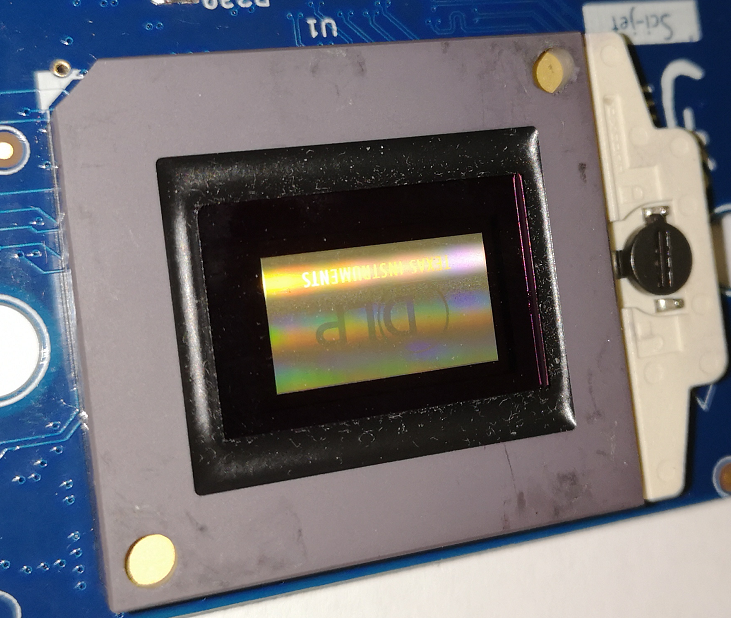

On my design ,you can hardly find a clear viewing angle,and the grayscale contrast is very poor:

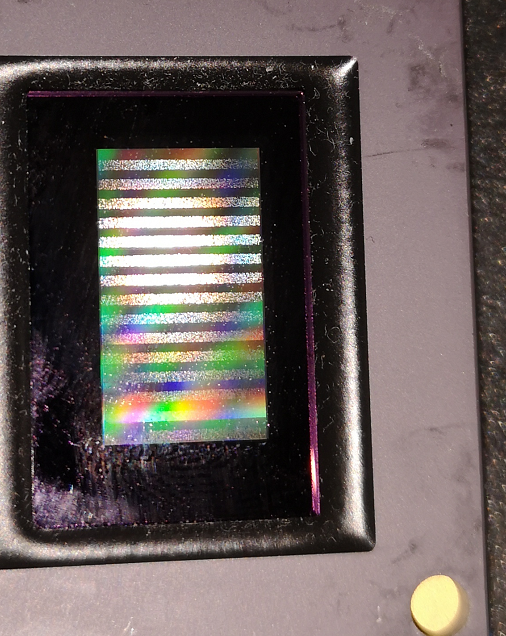

most of the viewing angles are like this,as in the red box, there are some static bars. The blue box is faintly visible display text

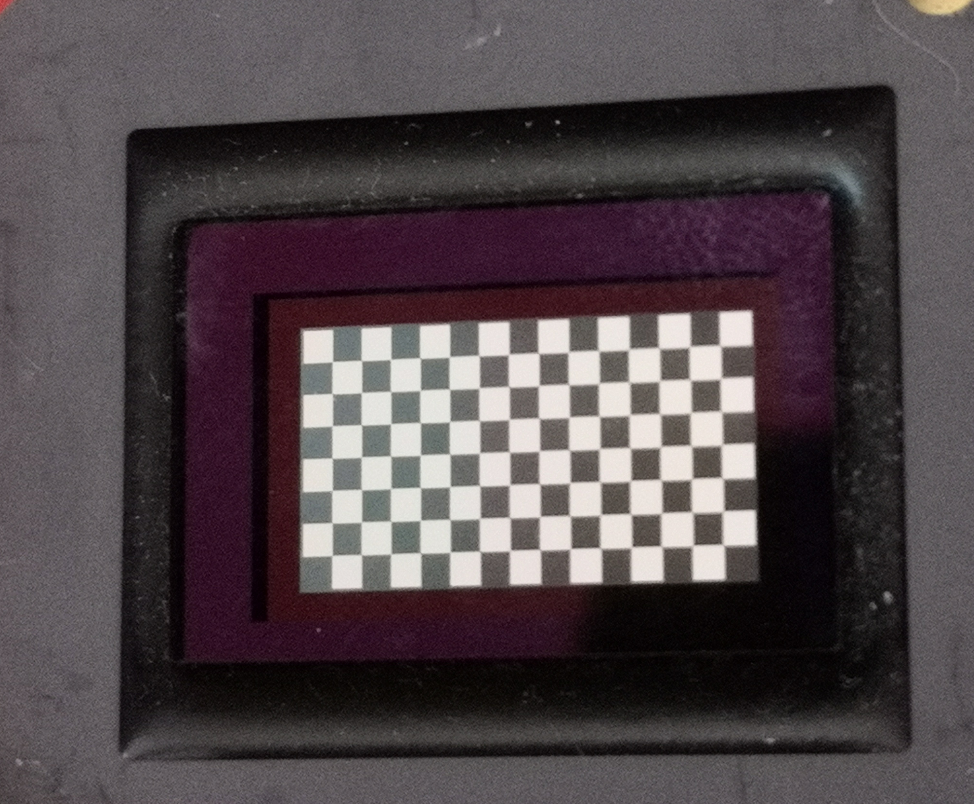

Display after turning off the power:

I measured several voltage signals of the DMD:

VCC & VCCI: 3.23 V

VOFFSET: 8.41 V

VRESET: -9.99 V

VBIAS: 16.24 V

The voltage signal looks like normal, i don't know how to start troubleshooting, I really need your help.

Best regards,

Byron