TI,

I am looking at using the DLPC300 controller for a system, I have experience driving the DDC3000 chipset and bit-plane driving for DMDs and have a question about Pattern Input mode.

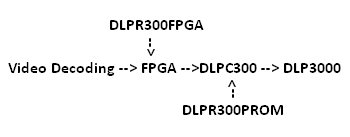

How is this mode achieved? I understand from "DLPU004" that Input Pixel Data Format needs to be set to 2, Input Resolution Command needs to be set to 35. I also understand from the DLPC300 datasheet that an optional DLPR300 programmed device can be added, it appears it controls the output plane order from the mDDR using RD_BUF(1:0) and Buffer_Swap.

Is there documentation that describes how to use Pattern Input mode without a DLPR300? The system I am working on could not accept the latency of:

Video Decoding --> App FPGA --> DLPR300 --> DLPC300 --> DMD

Thanks in advance for any help you could provide

Tom