Other Parts Discussed in Thread: DLPC3435,

Hi,

For DSI interfaces in many FPGAs it is required to use four pins for each DSI lane in order to facilitate the Bidirectional Low Power mode.

I know that the DLPC3435 doesn't support the Bidirectional, but I'm wondering about Low power. The documentation for DLPC343x states that the DSI clock lane must be in a low power state upon deassertion of RESETZ, and must remain in that state for 100us after.

My question is, does the DLPC3430 require the LP interface to be connected to any, all, or some subset of the lanes.

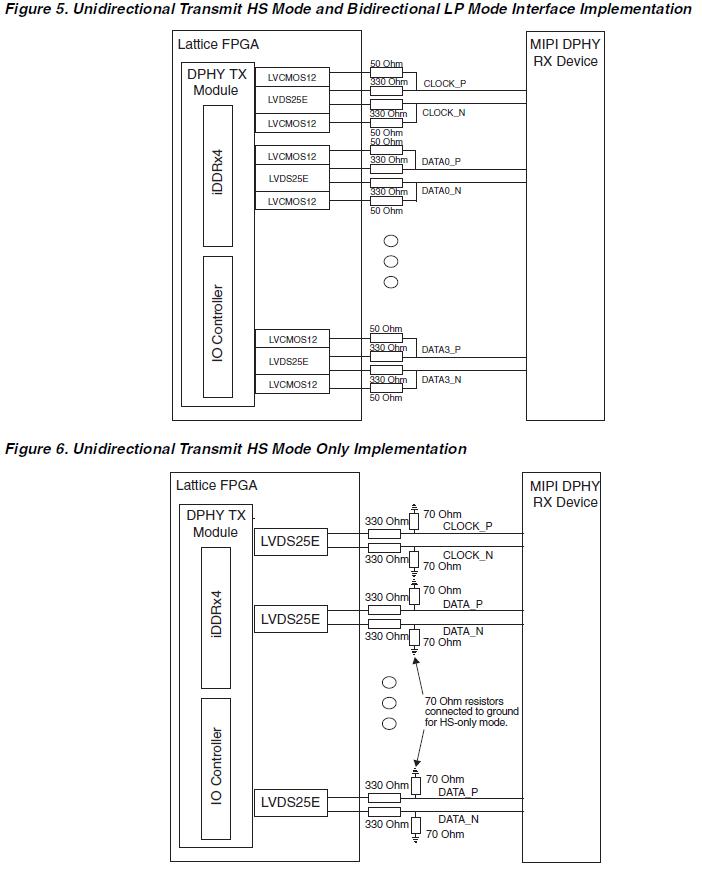

I've included a diagram, which is an example of driving a MIPI DPHY with a Lattice FPGA. In the top diagram (Figure 5) each lane is connect to 4 pins. 2 LVDS pins, and 2 LVCMOS pins, which facilitate the LP and Bidirectional functionality. The bottom figure is high speed only, and only connects the 2 LVDS pins.