IDE:CCS5.5

ChipSet:C5515 DSP

OS:WIN

Emulator:XDS100V1

Audio Settings: 16bit Little Endian,8000Sampling Rate

Problem:unable to listen playback through I2S via DMA

aic3204 settings: // Configure AIC3204 PAGE0 REG 1 = 1 // Reset codec USBSTK5515_wait_Test( 200 ); // Wait //Configure Power Supplies PAGE 1 REG 1 = 8 // Disable crude AVDD generation from DVDD REG 2 = 1 // Enable Analog Blocks, use LDO power // PLL and Clocks config and Power Up PAGE 0 REG 27 = 0x0d // I2S interface, 16 Bit, BCLK and WCLK is set as o/p ,DOUT High Impedence REG 28 = 0x00 // Data ofset = 0 REG 4 = 3 // PLL setting: PLLCLK <- MCLK, CODEC_CLKIN <-PLL CLK REG 6 = 4 // PLL setting: J = 4 REG 7 = 0x17 // PLL setting: HI_BYTE(D) REG 8 = 0xc0 // PLL setting: LO_BYTE(D) REG 30 = 0x88 // BCLK N Divider ->> DAC_CLK/N =(12288000/8) = 1.536MHz = 32*fs REG 5 = 0xA4 // PLL setting: Power up PLL, P=2 and R=4 REG 13 = 0 // Hi_Byte(DOSR) REG 14 = 0x80 // Lo_Byte(DOSR) REG 20 = 0x80 // AOSR for AOSR = 128 ->> Use with PRB_R1 to PRB_R6, ADC Filter Type A) REG 11 = 0x80+36 // Power up NDAC and set NDAC value to 36 REG 12 = 0x83 // Power up MDAC and set MDAC value to 3 REG 18 = 0x80+36 // Power up NADC and set NADC value to 36 REG 19 = 0x83 // Power up MADC and set MADC value to 3 // DAC ROUTING and Power Up PAGE1 REG 12 = 0x08 // LDAC AFIR routed to HPL REG 13 = 0x08 // RDAC AFIR routed to HPR PAGE0 REG 64 = 0x02 // Left vol=right vol REG 65 = 0x00 // Left DAC gain to 0dB VOL; Right tracks Left REG 63 = 0xd4 // Power up left,right data paths and set channel PAGE1 REG 16 = 6 // Unmute HPL , 6dB gain REG 17 = 6 // Unmute HPR , 6dB gain REG 9 = 0x30 // Power up HPL,HPR

I2S2 settings

short USBSTK5515_I2S_init(void)

{

/* I2S settings */

I2S2_SRGR = 0x0;

I2S2_CR = 0x8010; // 16-bit word, slave, enable I2C

I2S2_ICMR = 0x3f ; // Disable interrupts 0x3f for enable

return 0;

}

dma settings: PlayBuf = &g_DMA_PlayingBuf[0]; DMA1CH0TCR2 = 0x0204 ;// DMA_EN = 0, Destn Addr = Constant, Source Add Auto Inc, Sync Mode src_add_P = (Uint32)PlayBuf ; if((src_add_P >= CSL_DMA_DARAM_START_ADDR) && (src_add_P <= CSL_DMA_DARAM_END_ADDR)) src_add_P = (src_add_P << 1) + 0x010000 ;//BYTE ADDRESS TO DMA else if((src_add_P >= CSL_DMA_SARAM_START_ADDR)&& (src_add_P <= CSL_DMA_SARAM_END_ADDR)) src_add_P = (src_add_P << 1)+ 0x080000 ;// BYTE ADDRESS TO DMA DMA1CH0SSAU = (Uint16) (src_add_P >> 16) ; DMA1CH0SSAL = (Uint16) src_add_P ; // Dest Address = I2S0 Address, No Inc DMA1CH0DSAU = 0 ; DMA1CH0DSAL = 0x2A0C ; //I2S2_W1_LSW_W Right Channel Tx Register Address of I2S2 //event sync.. // Select Event I2S2 to Trigger DMA in DMAnCESR DMA1CESR1 = 0x0601 ; DMA1CESR2 = 0x0000 ; DMA1CH0TCR1 = DMA_PLAYBACK_BUFFER_SIZE * 4 ; // Length = 240 DMA1CH0TCR2 = 0x0204 ;// DMA_EN = 0

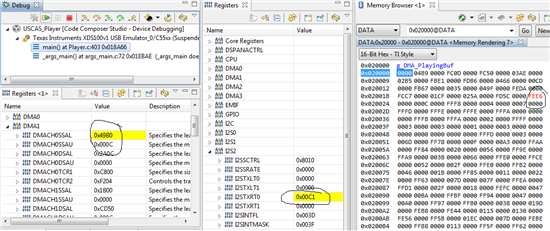

despite of all proper settings also i am not able to acquire valid data from my HPR/HPL,when debugged while i was writing a particular data to the dma playback buffer i am not seeing the same data in the transmit register i.e, the dma is taking wrong data from its address,if you see the screen shot i have attached you can see the buffer content and the content at the tx register of that particular channel ,

when i have loaded the address it was properly loaded the

byte address = 0x020000 << 1 + 0x080000 =>0xC0000 but

,on every step in i am finding the DMA src address increment in unevenly why so ? should nt it be increment by 4 ?

is that a debugger problem ?

what is the solution to my problem,am i using a wrong dma settings or what ? i really doubt on address the DMA is referring to !

PS:my playback dma buffer is of size 50kB located in SARAM from x00040000 to x0004C800

ScreenShots:

if any sample projects are available you can link them where i can follow up the settings