I'm seeing strange behaviour with the C5535 PLL multiplier. I noticed a small error in my output frequency, so tried a range of configuration values and got a dodgy result. I'm using the RTC as the system clock source, with a 32.768 kHz oscillator. My PLL register settings are:

CGCR2 0x8000 (RD BYPASS = 1)

CGCR3 0x080E (default)

CGCR4 0x0201 (OUT DIV ENABLED, OD = 1 (so pll out gets devided by 2))

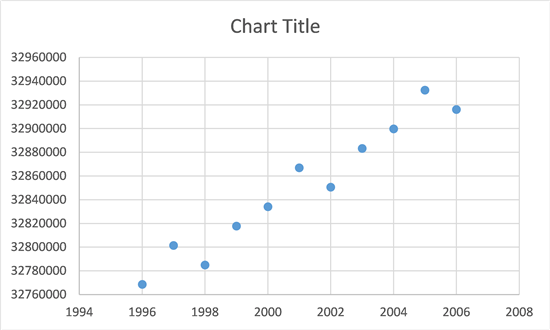

I have tried a range of values for M in CGCR1 and measured the corresponding frequency at CLKOUT. results are:

M vs f (hz)

2006 : 32916050

2005 : 32932450

2004 : 32899710

2003 : 32883310

2002 : 32850540

2001 : 32866910

2000 : 32834180

1999 : 32817750

1998 : 32784970

1997 : 32801370

1996 32768610

If you plot this it looks like a sawtooth instead of a straight line (see below).

Am I missing something, or is this a hardware bug?