Dear All,

I've a question about the transmit clock polarity of C5509's McBSP2 working as SPI Slave.

I'd like to configure my C5509A's McBSP2 as SPI Slave and set the polarity of its CLKX & CLKR to what described in:

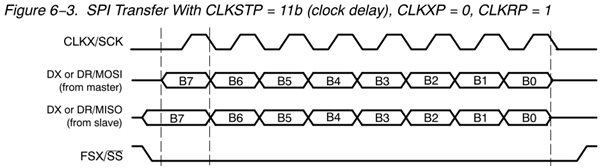

Figure 6−3. SPI Transfer With CLKSTP = 11b (clock delay), CLKXP = 0, CLKRP = 1 of TMS320VC5501/5502/5503/5507/5509/5510 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide (SPRU592E).

In such configuration, I expect:

1. McBSP2's Receiver samples data on clock's rising edge and

2. McBSP2's Transmitter transmits date on clock's falling edge.

I believe that Receiver works as what I expected because in my program I can correctly receives the data from SPI Master.

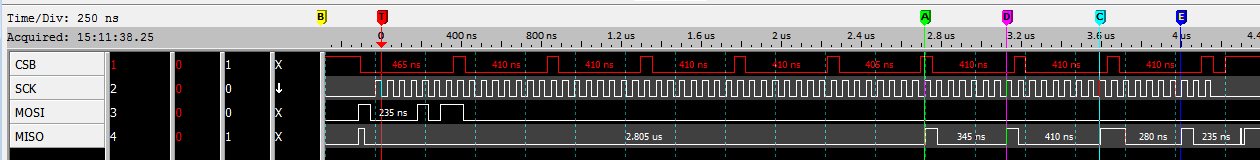

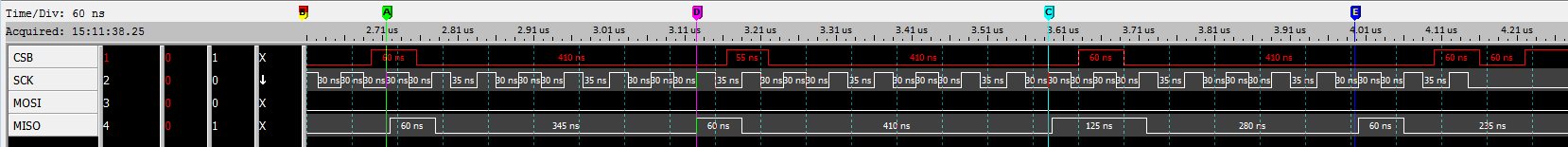

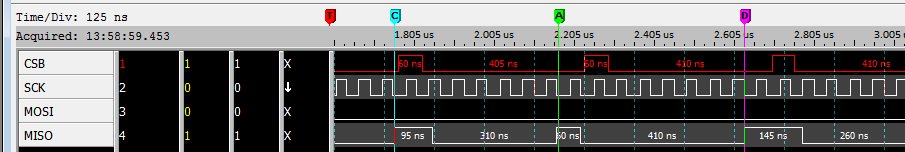

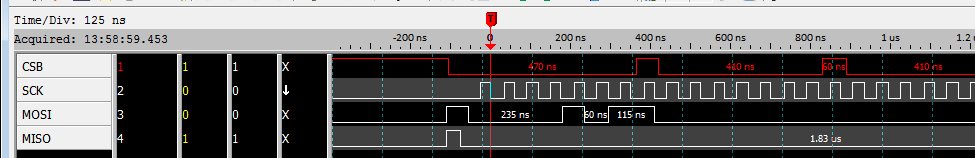

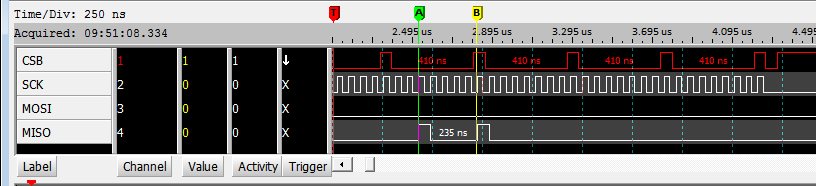

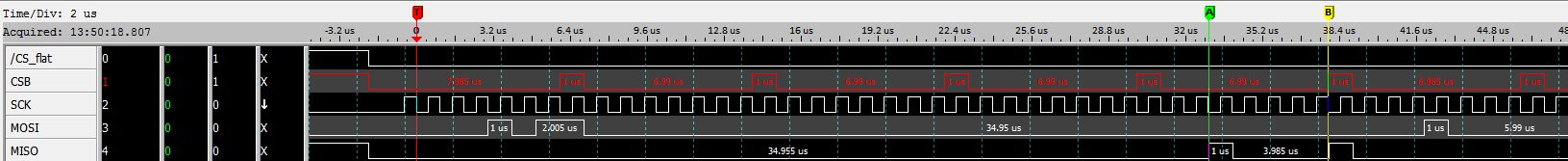

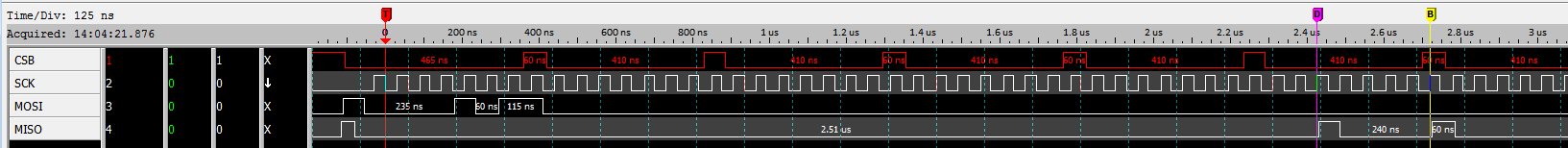

However, the Transmitter clock's polarity is not what I expected: It transmits data on clock's RISING edge instead of on falling edge. You should be able to see this in the following screen capture (MISO toggles right after SCK's positive edge):

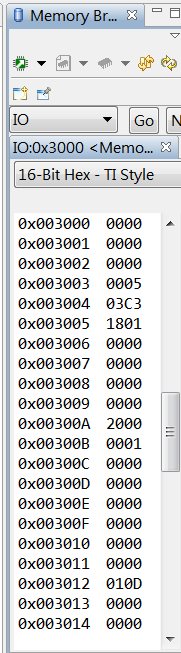

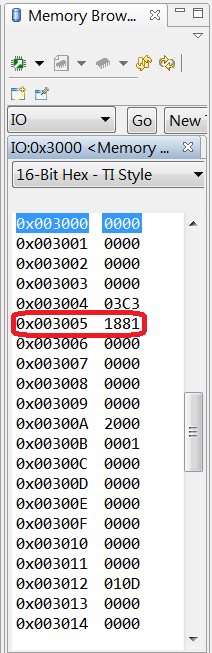

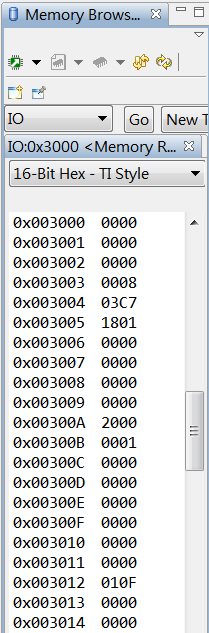

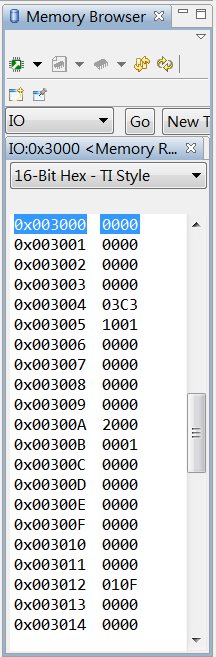

By checking the register in CCS I believe the following register settings are what I expected:

1. CLKSTP = 11b

2. CLKXP = 0

3. CLKRP = 1

I'll appreciate if anyone could advise why transmitter's clock polarity is not what I expected.

Thanks in advance!

Regards,

Oliver