I'm still struggling to get a McBSP DMA chain going with my C5510. The McBSP is working great when I manually read it with MCBSP_read32( hMcbsp ); When I try to trigger DMA transactions off of the RSYNC events from this McBSP port, everything goes awry. :( Here's the situation...

- McBSP0 hooked up to a serial ADC.

- FSR is the conversion clock for the ADC.

- The DR and CLKR pins are also hooked up to the ADC, and again, I can read the ADC just fine using MCBSP_read32()

- The McBSP is generating FSR, and CLKR using the Sample Rate Generator, and they're outputs.

- I've set up DMA transactions to source from the McBSP like so...

adc->dmaCfg.dmacssal = (DMA_AdrPtr)((Uint16)(MCBSP_ADDRH(adc->serial.hMcbsp, DRR1) << 1));

adc->dmaCfg.dmacssau = (Uint16) 0x0000;

- I've setup the destination address like so...

adc->dmaCfg.dmacdsal = (DMA_AdrPtr) (((Uint32)(demod->ring_start)<<1)&0xFFFF);

adc->dmaCfg.dmacdsau = (((Uint32) demod->ring_start) >> 15) & 0xFFFF;

- I've plugged my ISR into the dispatcher.

// Save off the event id.

adc->uiDmaEvtId = DMA_getEventId( adc->hDmaRx );

// Save off our callback function pointer

adc->fCb = callback;

// Map the event for DSP BIOS.

IRQ_map( adc->uiDmaEvtId );

adc->attrs.arg = (Arg)adc;

adc->attrs.ier0mask = 1;

adc->attrs.ier1mask = 1;

// Plug the ISR into the dispatcher along with its argument

HWI_dispatchPlug( adc->uiDmaEvtId, (Fxn)ADC_DMA_isr, &adc->attrs );

The DMAs never happen, and at first I thought it was because I had setup the ISR incorrectly, or hadn't appropriately enabled the IRQ or something. But then I started polling the SYNC bit of DMACSR, and it never goes high.

But here's where the plot thickens. If I do a manual read (MCBSP_read32), I get a SYNC event in my DMA engine. And I can do manual reads like that and watch the DMA counts increment as well. WHAT GIVES???

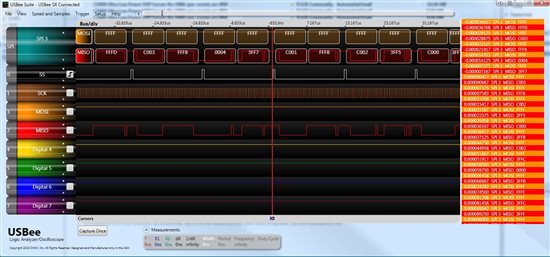

I've been wondering if maybe the fact that I'm sourcing the FSR and CLKR has anything to do with it. I have the McBSP in free running mode, so those lines are always going. (Verified with an LA.) Or I was wondering if DRR1 is still the appropriate address for the DMA since it's a 32-bit read, and DRR2 must be read first for data integrity issues. I don't know. I'm grasping at straws here. Anyone have any in-depth insight into the McBSP/DMA interactions in the C55xx series? Any help would be much appreciated. Thanks.

p.s. I do call DMA_start... see below

adc->state = ADC_DMA_RUNNING;

IRQ_globalDisable();

IRQ_clear( adc->uiDmaEvtId );

// Enable the interrupt associated with DMA0/ADC0

C55_enableInt( adc->uiDmaEvtId );

DMA_start( adc->hDmaRx );

IRQ_globalEnable();

// Start the port

MCBSP_start( adc->serial.hMcbsp, MCBSP_RCV_START | MCBSP_SRGR_START | MCBSP_SRGR_FRAMESYNC, 33 );