Hi TI Experts,

Please let me confirm the following question.

[Question]

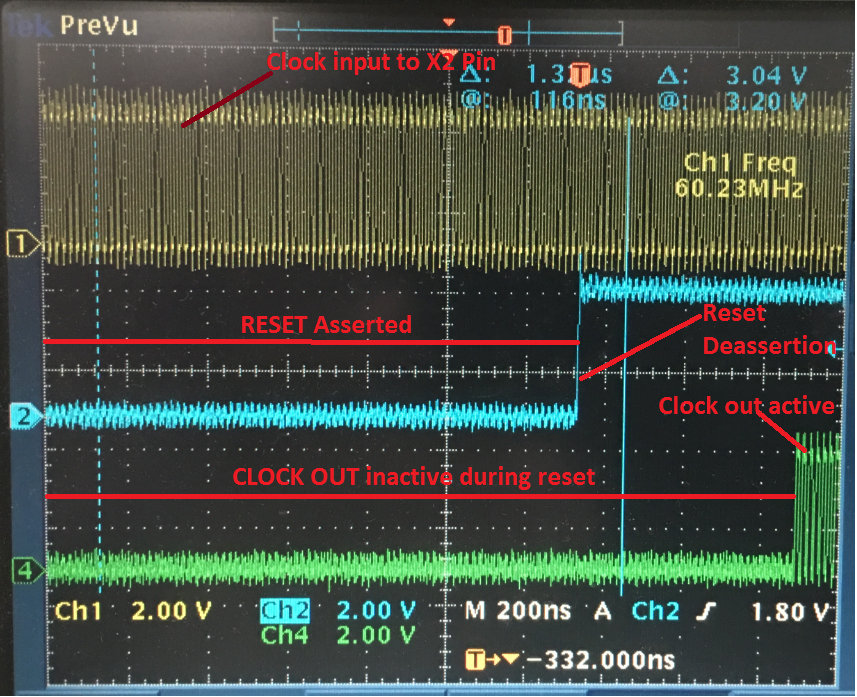

According to the datasheet, the nRESET pin release timing is R3 + R2 duration time.

Does the "CLKOUT" mean the actual pin?

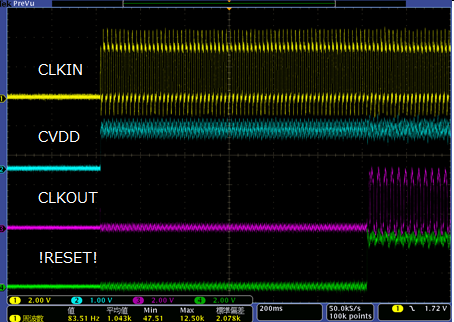

My customer said that the CLKOUT output was not generated during reset pin hold low. After releasing this pin, the CLKOUT was generated the signal. This is why they would like to know whether the CLKOUT description in Figure5-16 on datasheet is actually pin or not.

And can this device output the CLKOUT signal before releasing the nRESET pin?

Also, the following pin during nReset hold low was the following pin status.

EMU0/nOFF: High

EMU1: High

nTRST: Low

If you have any questions, please let me know.

Best regards.

Kaka