Hello,

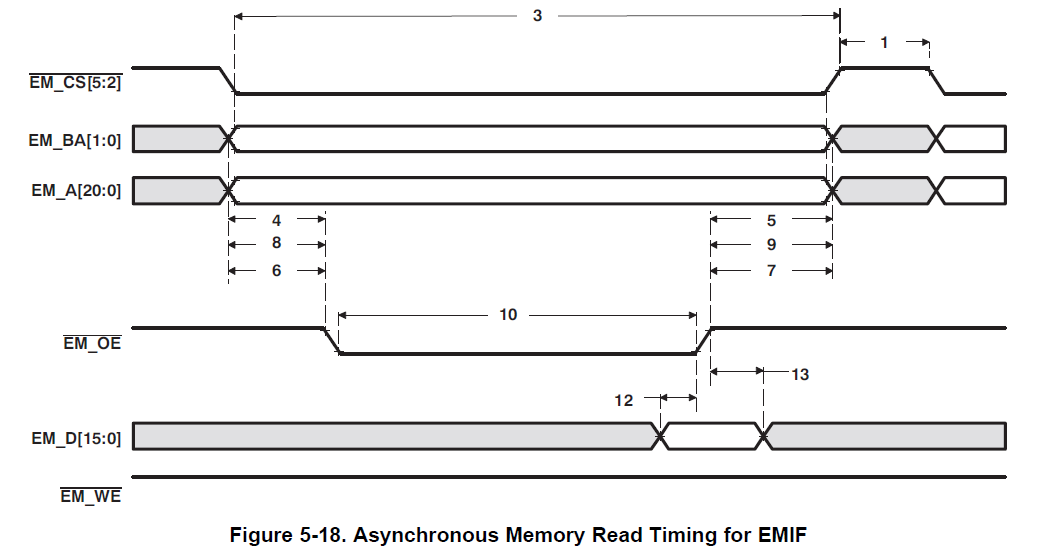

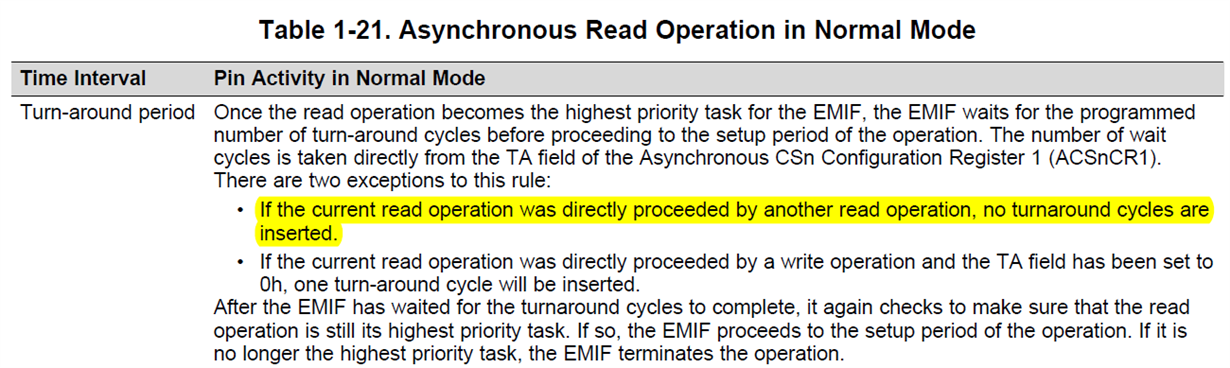

I am interfacing to a high-speed A2D with the C5515. The A2D has a parallel bus so I am using the EMIF to interface to it. The EMIF data sheet implies that I can set the RSETUP and RHOLD to 1 clock each, but in actuality 2 each is the minimum I can set it to. I can set RSTROBE to 1 clock. Am I missing something or is 2 clocks really the minimum?

Here are the register settings. I am using EM_CS2.

EMIF_ACS2CR2 = 0x3FFE; //Clear MSB of Rhold

EMIF_ACS2CR1 = 0x0001; //Rsetupclks = 1 (2), Rholdclks = 1 (2), Rstrobeclks = 1: 50ns, 20MHz

Chuck