Other Parts Discussed in Thread: ADS1278, SPRC100

Tool/software: TI C/C++ Compiler

Dear sir/mam,

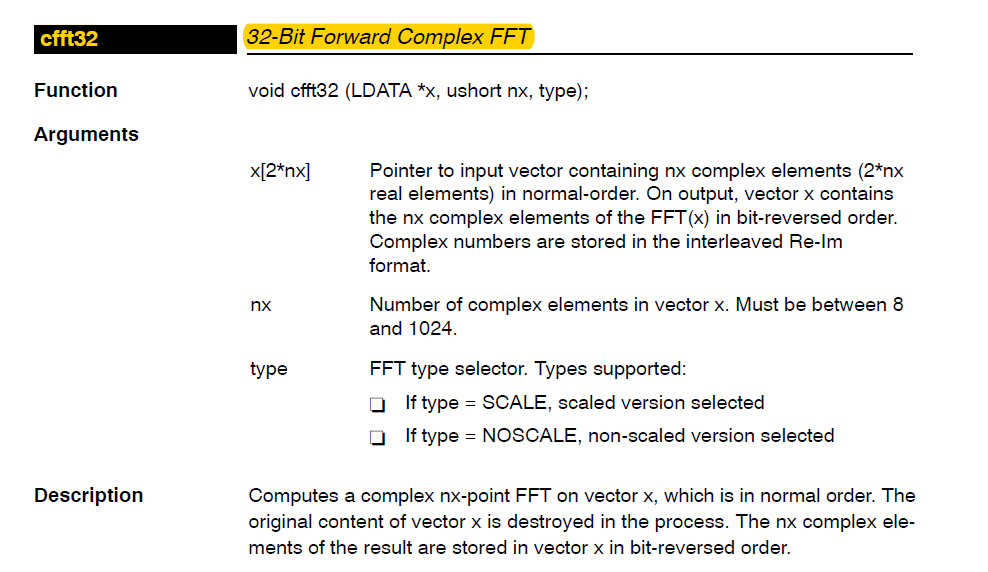

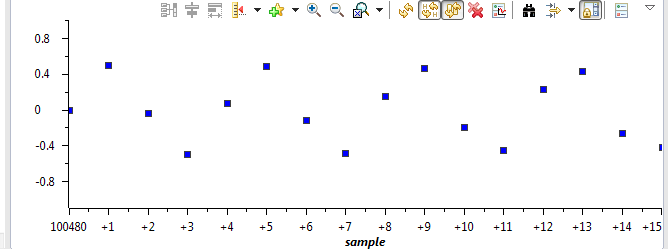

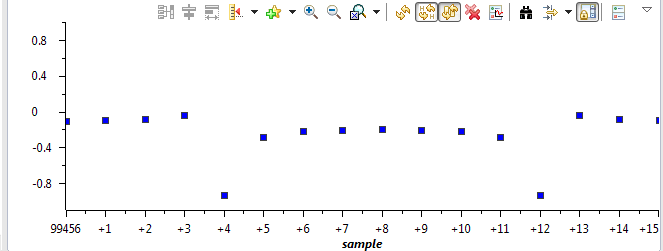

i am using hwafft library to calculate 1024 point fft.

Till now i have calculated fft for 10bit adc, 12 bit adc nad 16 bit adc..got very good results but for more accuracy.. i move forward for 24 bit adc (ads1278).

input provided 1.3v ref vtg=2.5v

sampling freq=50000.

but not getting the result this time.

i gone through SPRABB6B document...i got the point is real part is higher 16bit and imaginary are lower 16 bit.

but what if i get the real part is 24 bit? i will never show the correct result..just cross check i mask 24bit data to 16 bit data then appilied the fft and check the result..and got the correct result..

so does this mean that i CAN NOT apply more than 16bit of data to the FFT?

what else i can do

waiting for reply.