Tool/software: TI-RTOS

Hi,

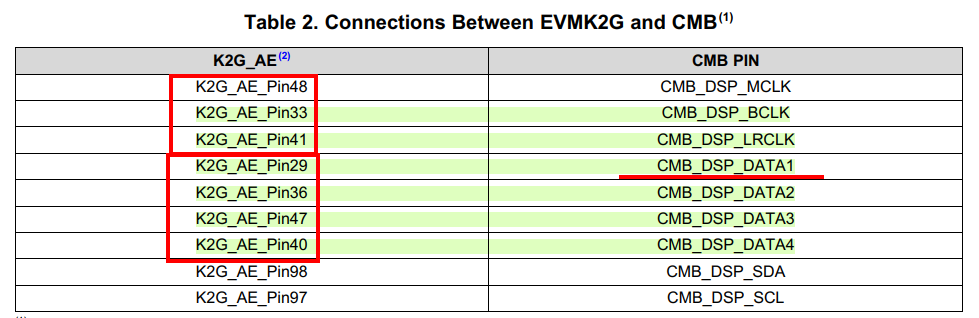

Thank you for your attention. We do project on K2GEVM board, based on the demo of K2G_bf_rt from the version SDK of processor_sdk_rtos_k2g_4_01_00_06.Our need is using McASP0 as Rx and McASP2 as Tx to get 8 mic signal through of 2 slices of PCM1864 codec and play one of 8 channels to the codec aic_3106 .

We are sure the configuration of codec PCM 1864 is correct because the data from PCM1864 is normal . The problem is configuration of McASP0, because there is no sound from Line Out( codec of AIC_3106)on the K2GEVM board .What we changed on McASP0 configuration of the demo K2G_bf_rt of hardware and software as the follow steps:

predef K2G_M001_A6x_Platform

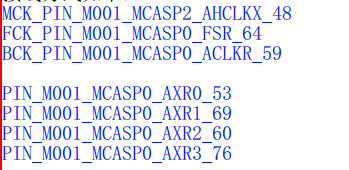

1. McASP0 pinmux

/////////////////////// Cmb_STATUS cmb_AudioInit(void) ////////////////////////////////

#ifdef K2G_M001_A6x_Platform

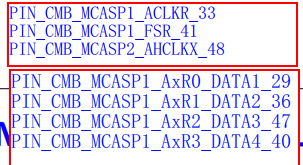

/* MCASP1ACLKX, MCASP1AFSX, - PADCONFIG 155 to 156, added by HeWujun 2018.4.12 */

cmb_padMax = 156;

for (cmb_padCfg = 155; cmb_padCfg <= cmb_padMax; cmb_padCfg++)

{

cmb_pinMuxSetMode(cmb_padCfg, CMB_PADCONFIG_MUX_MODE_QUINARY);

// set to weak pull down

cmb_pullSetMode(cmb_padCfg, 0);

}

/* MCASP1AMUTE - PADCONFIG 158 */

cmb_pinMuxSetMode(158, CMB_PADCONFIG_MUX_MODE_QUINARY);

// set to weak pull down

cmb_pullSetMode(158, 0);

#endif

/* MCASP1AHCLKX - PADCONFIG 157 */

cmb_pinMuxSetMode(157, CMB_PADCONFIG_MUX_MODE_QUINARY);

// set to weak pull down

cmb_pullSetMode(157, 0);

////////////////////////////////////////////////////////////////////////////////

/* MCASP1AXR[0:3] - PADCONFIG 159 to 162 */

cmb_padMax = 162;

for (cmb_padCfg = 159; cmb_padCfg <= cmb_padMax; cmb_padCfg++)

{

cmb_pinMuxSetMode(cmb_padCfg, CMB_PADCONFIG_MUX_MODE_QUINARY);

// set to weak pull down

cmb_pullSetMode(cmb_padCfg, 0);

}

#ifdef K2G_M001_A6x_Platform

/* MCASP1AXR[4] - PADCONFIG 163, for DAC 3106 */

cmb_padMax = 163;

cmb_pinMuxSetMode(cmb_padCfg, CMB_PADCONFIG_MUX_MODE_QUINARY);

// set to weak pull down

cmb_pullSetMode(cmb_padCfg, 0);

#endif

//////////////////////////////////////////////////////////////////

2 .revise status = eDmaConfig() function and add handle to eDMA0;

////////////////// status = eDmaConfig() //////////////////////////

EDMA3_DRV_Result edmaResult = 0;

uint32_t temp;

// uint32_t temp0 ;

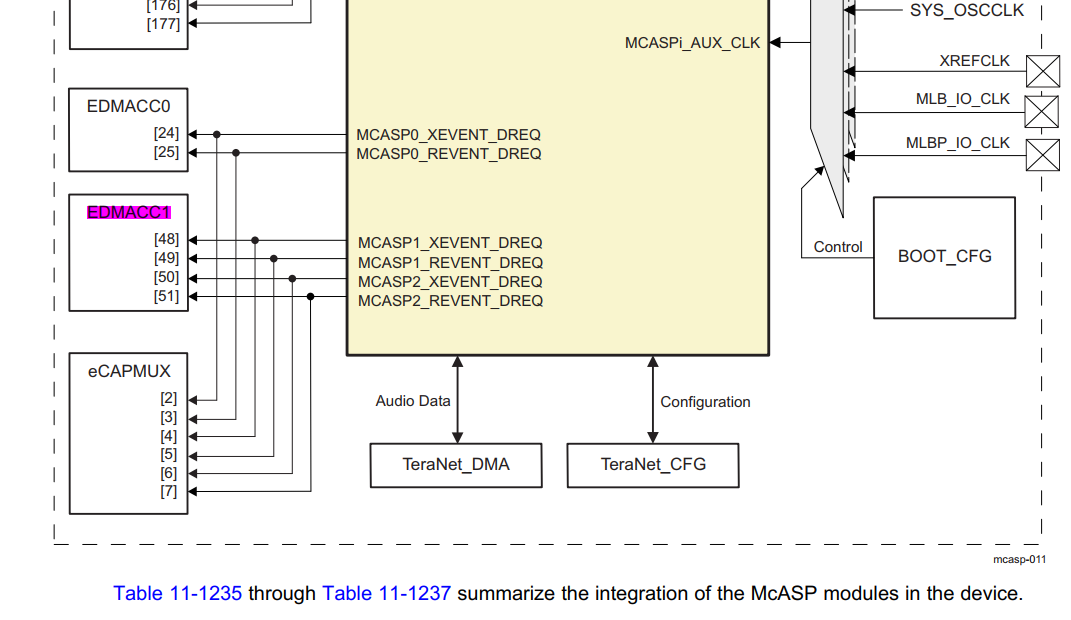

#ifdef K2G_M001_A6x_Platform

/* Enabling the dmaChannel MCASP1 Events to EDMACC1 (48 & 49) and

* Enabling the dmaChannel MCASP2 Events to EDMACC1 (50 & 51) */

temp=sampleEdma3GblCfgParams[1].dmaChannelHwEvtMap[1];

sampleEdma3GblCfgParams[1].dmaChannelHwEvtMap[1]= temp | 0x000F0000;

/* Enabling the dmaChannel MCASP0 Events to EDMACC0 (24 & 25) */

temp=sampleEdma3GblCfgParams[0].dmaChannelHwEvtMap[0];

sampleEdma3GblCfgParams[0].dmaChannelHwEvtMap[0]= temp | 0x03000000;

#else

/* Enabling the dmaChannel MCASP2 Events to EDMACC1 (50 & 51) */

temp=sampleEdma3GblCfgParams[1].dmaChannelHwEvtMap[1];

sampleEdma3GblCfgParams[1].dmaChannelHwEvtMap[1]= temp | 0x000C0000;

#endif

/* Initialize eDMA 0 */

hEdma0 = edma3init(CSL_EDMACC_0, &edmaResult);

if((hEdma0 == NULL) || (edmaResult != 0))

{

IFPRINT(cmb_write("eDMA instance 0 Initialization Failed\n"));

IFPRINT(UART_printf("eDMA instance 0 Initialization Failed\n"));

return (Cmb_EFAIL);

}

/* Initialize eDMA 1 */

hEdma1 = edma3init(CSL_EDMACC_1, &edmaResult);

if((hEdma1 == NULL) || (edmaResult != 0))

{

IFPRINT(cmb_write("eDMA instance 1 Initialization Failed\n"));

IFPRINT(UART_printf("eDMA instance 1 Initialization Failed\n"));

return (Cmb_EFAIL);

}

///////////////////////////////////////////////////////////////////////////////////////

/* Handle to eDMA */

extern EDMA3_DRV_Handle hEdma1;

/* added by HeWujun 2018.4.13 */

#ifdef K2G_M001_A6x_Platform

extern EDMA3_DRV_Handle hEdma0;

#endif

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////