Hello,

I am evaluating 66AK2H12/06.

Are there any restriction to enable VFP in CortexA15 cpu1, cpu2, cpu3?

I perform following source code to enable VFPU.

Although CortexA15 cpu0 can return check flag correctly, other CPUs(cpu1, cpu2, cpu3) can not .

( I am not sure if undefined instruction exception is occured, or not, because I have not been able to connect debugger to K2HEVM. )

reset_entry

if (master_core) {

// Arm boot magic address configuration

*(unsigned int *)0x0C5AD004 = reset_entry;

// cpuX domain Next State. Powered ON configuration

*(unsigned int *)0x01E80414 = 0;

// Power domain transition command

*(unsigned int *)0x01E8040C = 1;

}

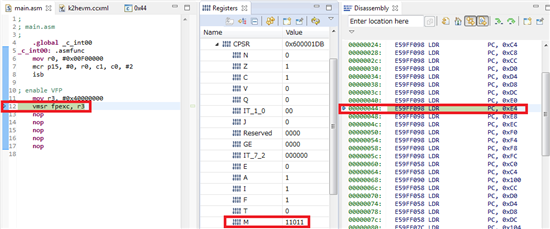

// enable to access for CP10 & CP11 (VFP)

mov r0, 0x00F00000

mcr p15, 0, r0, c1, c0, 2

isb

// enable VFP

mov r3, #0x40000000

vmsr fpexc, r3

//Check flag

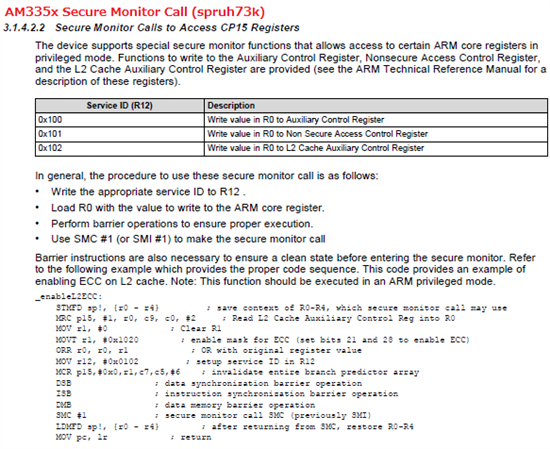

Reference document:

・spruhj4.pdf

->KeyStone II Architecture ARM CorePac User Guide

(P28) 2.5 VBUSP Memory-Mapped Registers

・ARM ® Cortex ® -A15 MPCore ™ Processor Revision: r4p0 Technical Reference Manual

->14.2.2 Enabling Advanced SIMD and VFP extensions

->Using the Advanced SIMD and VFP in Secure state only

If there are any restrictions, please let me know.

Best regards, RY