I've a problem with the shared memory of my C6678.

I'm sending data from another DSP via SRIO to the Shared Memory of My DSP and i want to check if the data are correct

This is the simple test function i'm using

CRandGen::SetSeed(Tcount+1); //Pseodo random generator

DstAddress = (UINT32*)(aSHARED_MEMORY_BASE + PktSize);

for (int j = 0; j < PktSize/4; j++)

{

UINT32 Read = DstAddress[j];

UINT32 Check= CRandGen::Rand();

if(Read != Check)

Ecount++;

}

I've put a breakpoint at the row DstAddress = (UINT32*)(aSHARED_MEMORY_BASE + PktSize);

In my first run DstAddress = 0x0c000000 and i get no problems

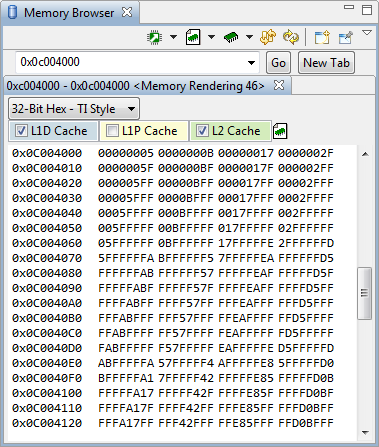

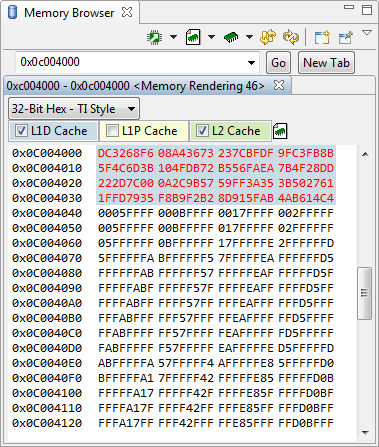

In the second run DstAddress = 0x0c004000 and when i reach the breakpoint the data in the shared memory is correct. But if i proceed step by step when i reach the row UINT32 Read = DstAddress[j]; the readen value is wrong and i see in the watch window the data changed with wrong values.

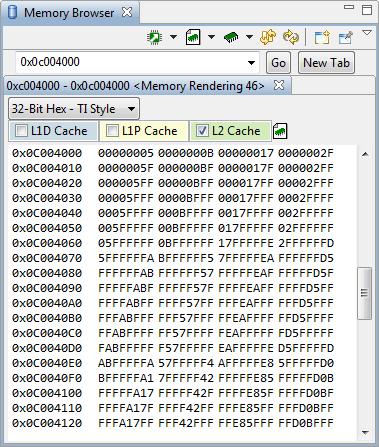

But if i deselect the L1D Cache combobox the data returns to the correct value.. So the data in the cache is wrong and the core uses this wrong values

What could be the problem that causes this coherence problem?