Hi all,

I met a problem about cache coherence when L1D is cacheable on C6670.

My code is base on sys/bios 6.33, C6670 and CCSv5.3.

***************************************************************************************************

I just want to use a 256 bytes buffer on MSMC and use core0 writes this buffer and then the core0 inform core1 to print this buffer on CCS's console.

**************************************************************************************************

To do this, my code flow is below

1). Define a global buffer MSMC_test

#defineMSMC_test_len 256

#pragma DATA_ALIGN (MSMC_test, 64) // to align with the L1D cache line

#pragma DATA_SECTION (MSMC_test, ".shareMemotest");

unsigned char MSMC_test[MSMC_test_len];

in the CMD file

.shareMemotest load >> MSMCSRAM

2). Before the tasks runs, I set L1P, L1D cacheable but L2 not.

CACHE_setL1PSize(CACHE_L1_32KCACHE);

CACHE_setL1DSize(CACHE_L1_32KCACHE);

CACHE_setL2Size(CACHE_0KCACHE);

3). Core0 writes the MSMC_test[0~256] then write-back-invalidates the L1D on Core0

for(i=0;i<MSMC_test_len;i++)

MSMC_test[i] = test_cnt;

CACHE_wbInvL1d ((void *) MSMC_test, MSMC_test_len, CACHE_WAIT);

4). Then the core0 send a notification to Core1.

5). Then Core1 invalidates the L1D on Core1 and print the MSMC_test[0~256] on the console

CACHE_invL1d((void *) MSMC_test, MSMC_test_len, CACHE_WAIT);

for(i=0;i<MSMC_test_len;i++)

{

System_printf("%d ",MSMC_test[i]);

if(i%20 == 0)

System_printf("\n");

}

**************************************************************************************************

My problem

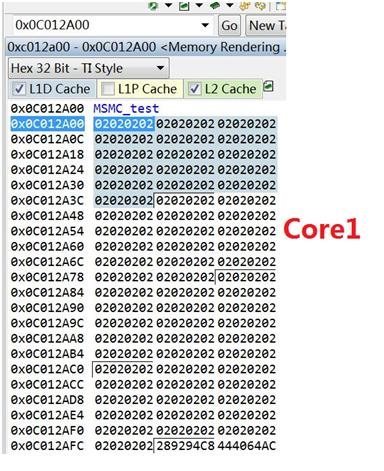

1. In the 5) step, when the Core1 prints the MSMC_test[0~127], all things go correct. I can get the correct results on console and the Memory Broswer is below

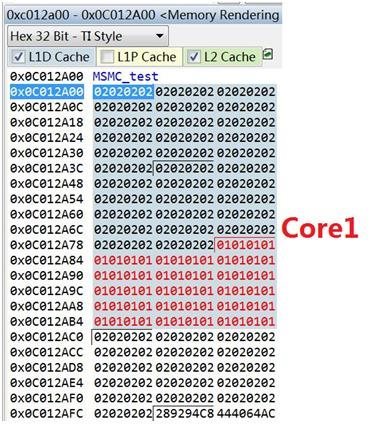

2. But when the Core1 prints the MSMC_test[128], the Memory Broswer shows the MSMC_test[128~191] changes to the last data like below (to begin with, Core0 writes 0x01 to MSMC_test[0~256] and the second time Core0 writes 0x02 to MSMC_test[0~256])

So I can not get the correct on console.

***************************************************************************************************

Could anyone help me!

Regards,

Feng