Hi,

I have questions about main PLL and DDR PLL on 66AK2H12/06.

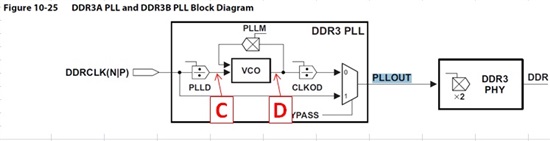

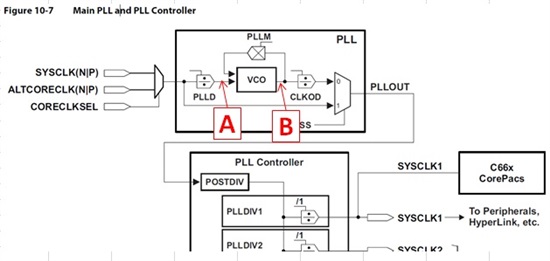

Please refer to the following figure. It is an excerpt from the data sheet(SPRS866E).

1. Does PLLD output of main PLL (at point A) has constraints of frequency range ?

2. Does VCO output of main PLL (at point B) has constraints of frequency range ?

3. Does PLLD output of DDR3 PLL (at point C) has constraints of frequency range ?

4. Does VCO output of DDR3 PLL (at point D) has constraints of frequency range ?

Best regard

H.U