Hi

I'm trying to boot the C66557 EVM from PCIe.

First I'm loading the pcieboot_ddrinit example successfully from Code Composer (.out file).

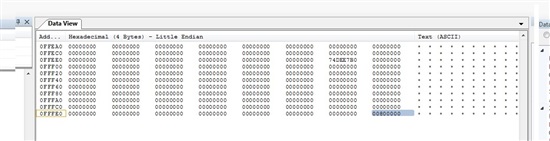

Then I see that the code monitors the Boot Magic Address, so then I load the binary code of my main program via PCIe into L2 Core 0, I know that I'm doing it OK because I've compared my binary to the memory dump from code composer.

The size of my program is 1MB (which is the size of L2 Core 0) and I want my program to start from 0x80000, so I write to the last 4 bytes (which is the Boot magic address) the 0x80000 value.

I then see that the DDR init example which monitors the Magic Address sees that it is not zero and performs

exit = (void (*)())entry_addr and entry_addr = 0x80000 ! , but following that nothing happens and the Program Counter is not at 0x80000 so my program clearly does not run.

Basicly what I want to do is to initialize the DDR and then continue running my program from L2 Core 0 and not the DDR.

Do I have to add my code to the pcieboot_ddrinit example ?