HI

I am trying to get the EMACBenchmark_ExampleProject to run on my custom board, which have a C6655 DSP and an Alaska Marvel 88E1512 PHY. I know that TI does not support other PHYs than the one on the EVM, but my problem is more related to the emac_drv than to the configuration and operation of the PHY.

I connect the ethernet port on my board directly to my PC and can see that the netcard in the PC detetct my board as a 1Gb Full duplex link. I have tested the example project out-of-the-box on the EVM and here it works perfectly and I can se on my PC that the EVM transmits alot of packets.

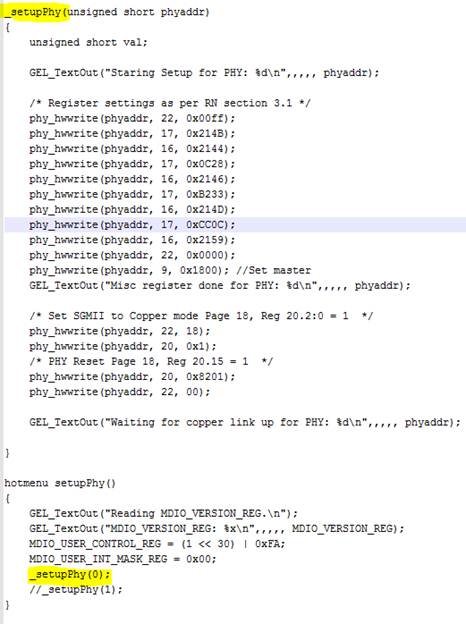

I have made a small modification to the example code from TI pdk_C6657_1_1_2_6. Instead of using the EVM value APP_PORT0_PHY_ADDR =24 I have changed this to APP_PORT0_PHY_ADDR = 1, which is what the PHY on my board have been configured to by HW.

I have also changed the destination MAC address to match the netcard on my PC so I can see if the board sends any packets.

When I run the code the app_send_task calls emac_open with these parameters

And inside emac_open the function SGMII_config is called with this config

I have also tried with masterEn=1 but that did not change anything

After calling sgmii_config the code waits for SGMII_STATUS.LINK to be 0

/* wait for the Link to Come Up */

do

{

stat = SGMII_REGS->STATUS;

stat = stat & 0x1;

} while( stat != 0x1 );

But that never happens so the program never returns from emac_open.

When I look at the registers in the SGMII modules I see the following values

this clearly shows that bit 0 in SGMII->status is not set, so SGMII does not detect that the link is up.

If I look in the registers from the MDIO module I see these values

which shows that the MDIO module have detected that there is a PHY on address 1 that have Link up.

So the question is

How come the SGMII module does not see the Link is up, when the MDIO module detects a PHY with link up?

I hope somebody can explain me how to modify the example so the SGMII detects that the link is up.

Best

Jens