I've seen this discussed quite a bit, but none of the posts helped resolve my problem.

I have a custom board with a C6655 connected to an Etron EJ198 over PCIe. Link training fails in state Polling.Compliance. I can see on a scope the receiver detect pulses coming from the DSP and if I put the Etron in reset then the receive detect stops on a failure.

I have 100nF caps in all the PCIe lanes with lengths matched and impedance controlled.

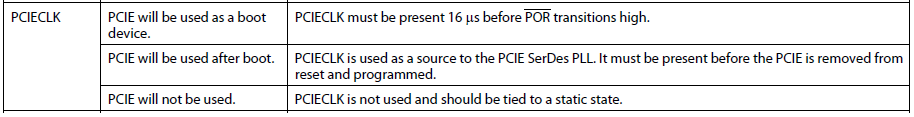

There seems to be a common thread of a clocking issue causing this problem. I'm using an Si52142 to generate the clock for the DSP and for the Etron. On a different prototype situation I used the same SI labs part to drive a clock to the Etron and to the 6657 EVM with success. The SiLabs part says that no termination resistors are required, so I have none. The outputs of the SiLabs part go through caps to the DSP for AC coupling. The other output goes directly to the Etron, just as it did on my previous prototype.

Could it be that there needs to be 50 ohm termination resistors to ground before the AC cap on the clock lines to the DSP? If so, could this lack of termination result in a link failure? When I try to link, I monitor the PLL lock bit and it is always set indicating that the PLL is locked.

Thanks

Jeff Allred