Hi,

I check the differential clock of USB_CLK on K2H EVM.

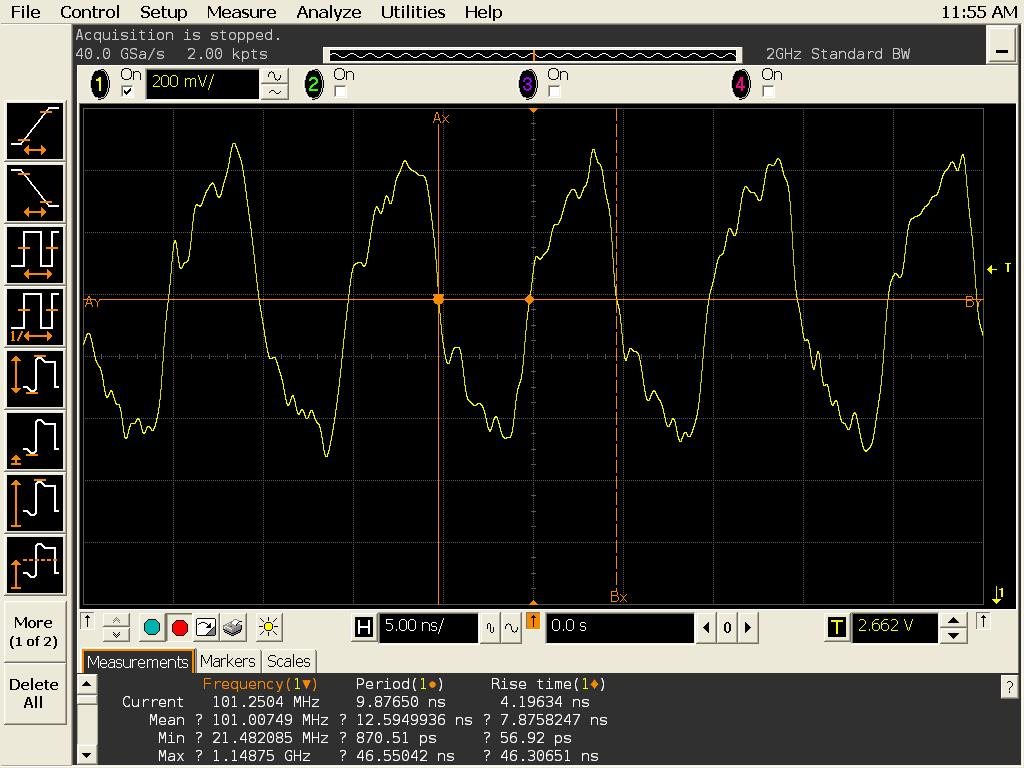

I confirmed output clock of CDCM6208(U19: Pin #29).

Please refer to the following image, USB_CLK is not like pulse wave.

USB_CLK(CDCM6208(U19: Pin #29))

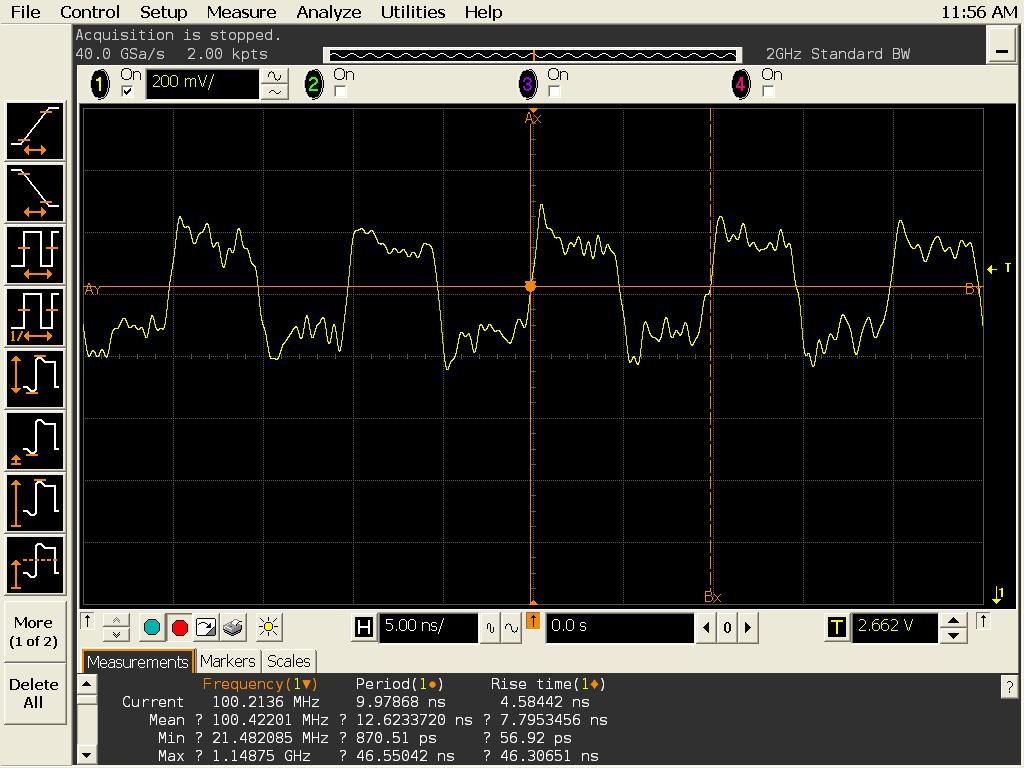

However, when I measured the DDR3A_CLK, it is observed pulse wave.

DDR3A_CLK(CDCM6208(U19: Pin #32)).

Why USB_CLK can not be observed pulse wave?

K2H EVM is not have AC-coupling capacitors at USB_CLKP/M.

Does differential clock of USB Phy not need AC-coupling?

Best regards,

H.U