Hi there.

Could someone explain what are for xmc_setup 4KB remapping procedure in evmc6678l.gel:

/* mapping for ddr emif registers XMPAX*2 */

XMPAX2_L = 0x100000FF; /* replacement addr + perm*/

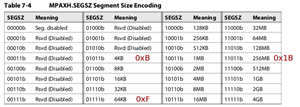

XMPAX2_H = 0x2100000B; /* base addr + seg size (64KB)*/ //"1B"-->"B" by xj

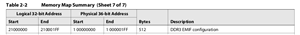

if in compliance with TMS320C6678 datasheet Table 2-2. Memory Map Summary 512 bytes of DDR3 EMIF configuration already mapped by default at 0x21000000 address?

And what does mean "seg size (64KB)*/ //"1B"-->"B" by xj" comment provided that

Thanks in advance.